# QOCVO

## ACT4751

### USB Fast Charger Power IC with 40V Input Voltage, 4A, Programmable Output Voltage and Current

#### **FEATURES**

- Certified USB Fast Charger, Reference Designs

- Qualcomm® Certified, Quick Charger Designs

- 4.5 V to 40 V Operational Input Voltage

- Programmable Output Voltage by I<sup>2</sup>C 3 V to 24 V in 12.5 mV Step

- Programmable Output Current Limit 4 A in 256 Step Resolution

- 450 kHz to 2.25 MHz Fixed-Frequency Current-Mode Control with External Clock Sync, 100% Duty Operation, Stable with MLCC

- · Out of AM Radio / Spread-Spectrum Operation

- 50 mΩ Integrated High-Side / Low-Side FETs

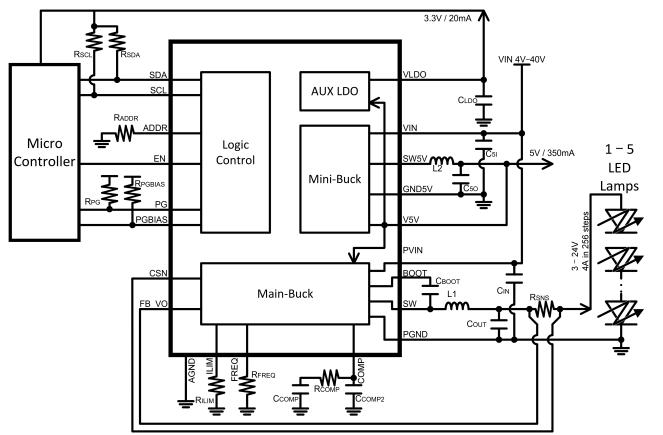

- 5 V / 350 mA Bias Buck Converter

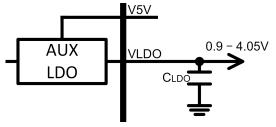

- 20 mA AUX LDO, Programmable Output Voltage

- I<sup>2</sup>C Interface, Fast-mode Plus (Fm+, 1 MHz) with Configurable Address

- Protections: UVLO, OVP, UVP (Hiccup/Latch-off), OCP, TSD

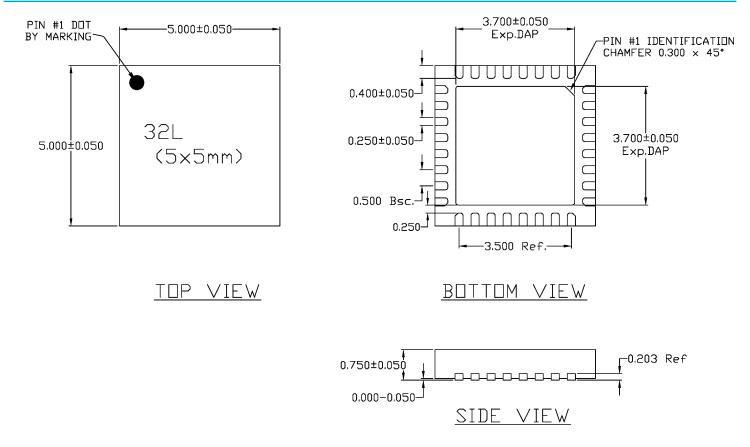

- Thermally Enhanced 5 mm × 5 mm QFN Package

### **APPLICATIONS**

- USB Fast Charger (PD 3.0 PPS)

- Quick Charge 4, Quick Charge 4+, Quick Charge 3.0

- Industrial Power Supply

- Infrastructure Power Supply

- High Power LED Lighting

ACT4751-101-REF03 (Test ID: 1100) USB Certified **Fast Charger** (USB PD 3.0 PPS) Reference Design: USB-C 80W × 1

### **GENERIC DESCRIPTION**

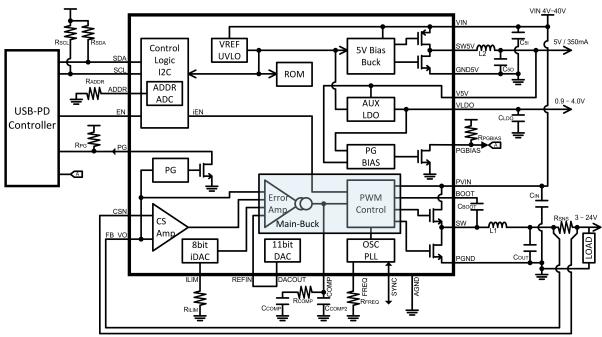

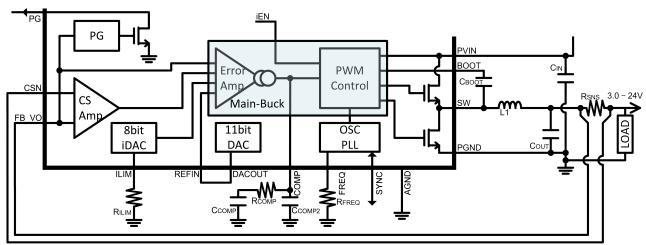

The ACT4751 is a programmable DC-to-DC buck converter with bias supply rails. This synchronous step-down voltage regulator supports a wide input voltage of 4.5 V to 40 V and integrates both the high side and low side MOSFETS. These  $50m\Omega$  R<sub>DSON</sub> transistors enable high efficiency by reducing power losses.

The ACT4751 main buck converter can be dynamically programmed to an output voltage between 3 V and 24 V in 12.5 mV steps via the  $I^2C$  or analog feedback. Also, it can dynamically program output current between 0 A to 4 A in 256 steps via the  $I^2C$  in a constant-current (CC) operation mode. The main-buck operates in a proprietary current mode control that supports external clock syncing for switching frequencies between 450 kHz and 2.25 MHz.

The ACT4751 is a perfect solution for USB Power Delivery 3.0 Programmable Power Supply (PD 3.0 PPS) charging applications. The ACT4751 integrates a 5 V / 350 mA mini-buck converter and a 20 mA AUX LDO to simplify application system designs. These rails can power up USB PD controllers and the 1.5W VCONN line in active USB-C cables.

The ACT4751 is available in a 32-pin 5mm x 5mm QFN package with a power optimized footprint and exposed pad for improved thermal performance.

ACT4751M-101-REF05 (QC20191223118) **4-Port** Total 280W: **Quick Charge 4** (USB-C 80W × 2) + **Quick Charge 3.0** (Type-A 60W × 2) (based on AEC-Q100 version device)

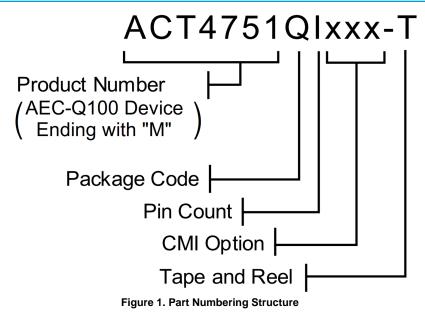

### **Ordering Information**

- 1. Standard product options are identified in this table. Contact factory for custom options, minimum order quantity required.

- 2. This device is RoHS Compliant and with Pb-free plating unless specified differently. The term Pb-free means semiconductor products that are in compliance with current RoHS (Restriction of Hazardous Substances) standards.

- 3. Package Code designator "Q" represents QFN

- 4. Pin Count designator "I" represents 32 pins

- 5. See the Factory Programming Options section for more information about CMI.

#### ACT4751 USB Fast Charger Power IC with 40V Input Voltage, 4A, Programmable Output Voltage and Current

|       |          |                   |          | User Prog                        | User Programmable Parameter Default            |                                   |                         |  |  |

|-------|----------|-------------------|----------|----------------------------------|------------------------------------------------|-----------------------------------|-------------------------|--|--|

| PART  | NUMBER   | Control<br>Scheme | AEC-Q100 | Output<br>Voltage <sup>[1]</sup> | Precise Output<br>Current Limit <sup>[2]</sup> | AUX LDO<br>Voltage <sup>[3]</sup> | DC-bias<br>Compensation |  |  |

| ACT47 | ′51QI102 | Current-mode      | —        | 5.0 V                            | 4 A                                            | 3.3 V                             | —                       |  |  |

<sup>⚠</sup>

⚠

$\odot$

Q

Q

Not all options are released, please contact your local sales representatives or customer.support@gorvo.com for a status and availability. Also, see Factory Programming Options.

#### **Similar Devices**

Following devices are similar to the ACT4751 device.

|               |                   |                 | User Prog                        |                                                |                                   |                         |

|---------------|-------------------|-----------------|----------------------------------|------------------------------------------------|-----------------------------------|-------------------------|

| PART NUMBER   | Control<br>Scheme | AEC-Q100        | Output<br>Voltage <sup>[1]</sup> | Precise Output<br>Current Limit <sup>[2]</sup> | AUX LDO<br>Voltage <sup>[3]</sup> | DC-bias<br>Compensation |

| ACT4752QI101  | Current-mode      | —               | 5.0 V                            | 4 A                                            | 3.3V                              | YES                     |

| ACT4751MQI101 | Current-mode      | YES,<br>Grade 1 | 5.0 V                            | 4 A                                            | 3.3V                              | YES                     |

|              |                   |                                  | Factory Pre-Programmed Fixed Settings |                                                |                                   |                         |  |

|--------------|-------------------|----------------------------------|---------------------------------------|------------------------------------------------|-----------------------------------|-------------------------|--|

| PART NUMBER  | Control<br>Scheme | Output<br>Voltage <sup>[1]</sup> | Output Current                        | Precise Output<br>Current Limit <sup>[2]</sup> | AUX LDO<br>Voltage <sup>[3]</sup> | DC-bias<br>Compensation |  |

| ACT4755QI101 | Current-mode      | 12.0 V                           | 4 A                                   |                                                | —                                 | YES                     |  |

| ACT4756QI101 | Current-mode      | 24.0 V                           | 4 A                                   | 4 A ±100 mA                                    | 3.3V                              | YES                     |  |

Not all options are released, please contact your local sales representatives or customer.support@qorvo.com for a status and availability. Also, see Factory Programming Options.

[1]: Upon requests, output voltage options are available from 3.0 V to 24.0 V in 12.5mV steps, where a minimum required quantity applies.

[2]: Upon requests, precise output current limit options are available from 1 A to 4 A in 15.6 mA steps, where a minimum required quantity applies.

[3]: Upon requests, AUX LDO voltage options are available from 0.9 V to 4.05 V in 50 mV steps, where a minimum required quantity applies.

### **Specifications**

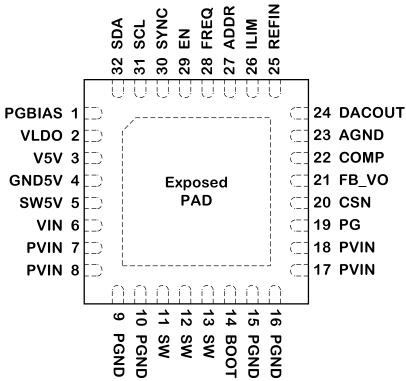

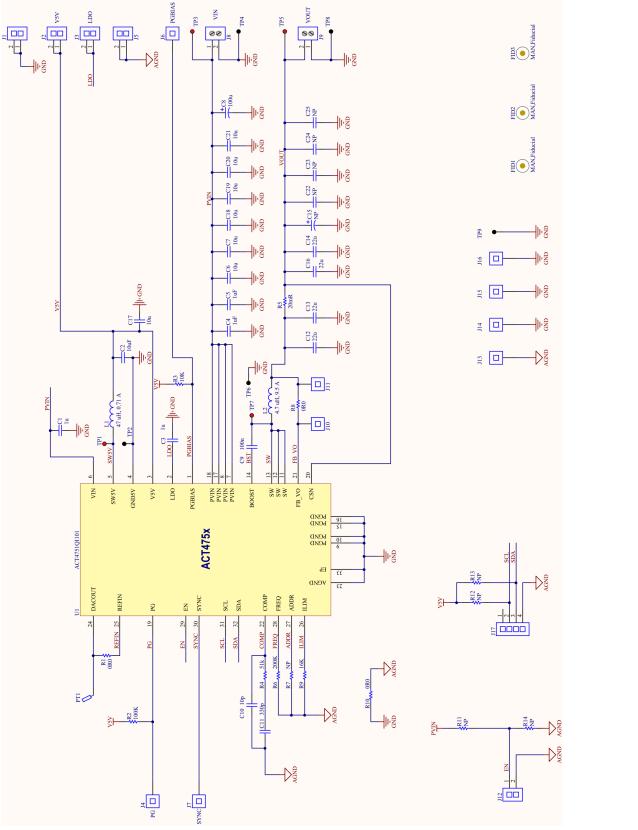

### **Pin Configuration**

Figure 2. 32-pin QFN, 5 mm ×5 mm, 0.5 mm pitch, TOP VIEW

#### **Pin Functions**

| PIN        | NAME   | DESCRIPTION                                                                                                                                                                                                                                                                     |

|------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

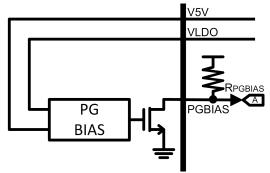

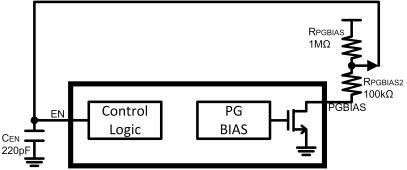

| 1          | PGBIAS | Power-good output of the Mini-buck Regulator and Auxiliary LDO. Open-drain and a pull-up resistor required. See PGBIAS Indicator Output.                                                                                                                                        |

| 2          | VLDO   | Output voltage node of the Auxiliary LDO. Connect a good quality, fixed value 1 µF capacitor between this pin and the GND5V pin. See Auxiliary LDO.                                                                                                                             |

| 3          | V5V    | 5 V bias supply to the device and voltage feedback of the Mini-buck Regulator. Connect two good quality capacitors in parallel, two 10 $\mu$ F and one 0.1 $\mu$ F between this pin and the GND5V pin. Place the 0.1 $\mu$ F capacitor with the minimum distance to the device. |

| 4          | GND5V  | Ground node for the Mini-buck Regulator.                                                                                                                                                                                                                                        |

| 5          | SW5V   | Switching node of the Mini-buck Regulator.                                                                                                                                                                                                                                      |

| 6          | VIN    | Power supply to the device. Connect a good quality 1 $\mu$ F capacitor, at least, between this pin and the GND5V pin. On a PCB, tied to the PVIN pin.                                                                                                                           |

| 7,8,17,18  | PVIN   | Power supply to the Main-buck Regulator. Connect good quality two 22 µF capacitors, at least, between this pin and the PGND pins, also tie to the VIN pin.                                                                                                                      |

| 9,10,15,16 | PGND   | Ground node for the Main-buck Regulator.                                                                                                                                                                                                                                        |

| 11,12,13   | SW     | Switching node of the Main-buck Regulator.                                                                                                                                                                                                                                      |

| 14         | BOOT   | Bootstrap capacitor node for the Main-buck Regulator. Connect a good quality, fixed value 0.1 $\mu$ F capacitor between this pin and the SW pin.                                                                                                                                |

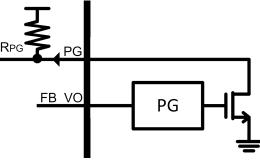

| 19         | PG     | Power-good output of the Main-buck Regulator. Open-drain and a pull-up resistor required.                                                                                                                                                                                       |

| 20         | CSN    | Current sense feedback input to the Main-buck Regulator. See Output Current Sensing.                                                                                                                                                                                            |

| 21         | FB_VO  | Voltage feedback input to the Main-buck Regulator. See Reference Voltage Input.                                                                                                                                                                                                 |

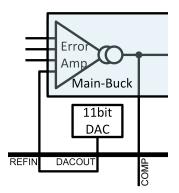

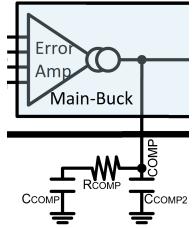

| 22         | COMP   | Error amplifier output. Connect a compensation network between this pin and the AGND pin.<br>See Main-buck Compensation Network.                                                                                                                                                |

| 23         | AGND   | Ground node for analog blocks of the device.                                                                                                                                                                                                                                    |

| 24         | DACOUT | Reference voltage output from the DAC. Usually, short to the REFIN pin. See Output Voltage Reference.                                                                                                                                                                           |

| 25         | REFIN  | Reference voltage input to the Main-buck Regulator. See Reference Voltage Input.                                                                                                                                                                                                |

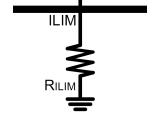

| 26         | ILIM   | Output current limit programming of the Main-buck Regulator. Connect a resistor between this pin and the AGND pin. See Output Current Reference.                                                                                                                                |

| 27         | ADDR   | I <sup>2</sup> C address selection. Connect a resistor between this pin and the ground. See I <sup>2</sup> C Address Selection.                                                                                                                                                 |

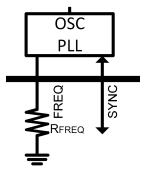

| 28         | FREQ   | Switching frequency programming of the Main-buck Regulator. Connect a resistor between this pin and the AGND pin. See Clock Generator.                                                                                                                                          |

| 29         | EN     | Enable logic input for the Main-buck Regulator. See Main-buck Enable Control.                                                                                                                                                                                                   |

| 30         | SYNC   | Clock synchronizing input/output for the Main-buck Regulator. See Clock Synchronizer.                                                                                                                                                                                           |

| 31         | SCL    | Clock port of the I <sup>2</sup> C Interface. Open-drain and a pull-up resistor required.                                                                                                                                                                                       |

| 32         | SDA    | Data port of the I <sup>2</sup> C Interface. Open-drain and a pull-up resistor required.                                                                                                                                                                                        |

| Expose     | ed PAD | Substrate contact for power dissipation. Connect to the PGND pins with a broad pattern.                                                                                                                                                                                         |

### **Absolute Maximum Ratings**

| PARAMETER                                                          | VALUE                                | UNIT |

|--------------------------------------------------------------------|--------------------------------------|------|

| PVIN, VIN                                                          | -0.3 to +48.0                        | V    |

| SW                                                                 | -0.3 to (PVIN + 1.0)                 | V    |

| FB_VO, CSN                                                         | -0.3 to +28.0                        | V    |

| Voltage difference between FB_VO and CSN                           | -0.3 to +0.3                         | V    |

| SW5V                                                               | -0.3 to (VIN + 1.0)                  | V    |

| BOOT                                                               | $(V_{SW} - 0.3)$ to $(V_{SW} + 6.0)$ | V    |

| PGND, GND5V, w.r.t. AGND                                           | -0.3 to +0.3                         | V    |

| EN, PG, PGBIAS, SYNC, REFIN, SDA, SCL, COMP, V5V (external supply) | -0.3 to +6.0                         | V    |

| Operation Junction Temperature ( $T_J$ )                           | -40 to +150                          | °C   |

| Storage Temperature                                                | -55 to +150                          | °C   |

| Lead Temperature (Soldering 10sec)                                 | up to +300                           | °C   |

⚠

Ŵ

Ŵ

Do not exceed these limits to prevent damage to the device. Exposure to absolute maximum rating conditions for long periods may affect device reliability.

All voltage values are with respect to the ground voltage unless otherwise specified.

#### **Recommended Operating Conditions**

| PARAMETER                                           | VALUE         | UNIT |

|-----------------------------------------------------|---------------|------|

| PVIN, VIN                                           | +4.2 to +40.0 | V    |

| V5V (External Supply)                               | +4.5 to +5.5  | V    |

| EN, PG, PGBIAS, SYNC, REFIN, SDA, SCL, COMP         | -0.3 to +5.5  | V    |

| Operation Junction Temperature (T <sub>J</sub> )    | -40 to +125   | °C   |

| Current Sensing Resistor (R <sub>CS</sub> )         | 5 to 80       | mΩ   |

| Frequency Programming Resistor (R <sub>FREQ</sub> ) | 40 to 200     | kΩ   |

All voltage values are with respect to the ground voltage unless otherwise specified.

#### **Package Thermal Information**

| PARAMETER                                                     | VALUE | UNIT |

|---------------------------------------------------------------|-------|------|

| Thermal Resistance, Junction to Ambient $(\Theta_{JA})^{[1]}$ | 24    | °C/W |

<sup>[1]</sup> Reference number, based on a real measurement of a ACT4751 evaluation board.

#### ACT4751 USB Fast Charger Power IC with 40V Input Voltage, 4A, Programmable Output Voltage and Current

#### **Electrical Characteristics**

PVIN = VIN = 12 V, V5V = 5 V (external supply), EN = 5 V,  $T_A = 25^{\circ}C$ , unless otherwise specified

| PARAMETER                            | SYMBOL                     | TEST CONDITION                                           | MIN  | TYP | MAX  | UNIT |

|--------------------------------------|----------------------------|----------------------------------------------------------|------|-----|------|------|

| BIAS BLOCK                           |                            |                                                          |      |     |      | ,    |

| VIN Mini-buck<br>Consumption Current | I <sub>I(VIN)</sub>        | EN = 0 V, V5V = 5.25 V, mini-buck ON and no switching    |      | 235 |      | μA   |

| V5V Quiescent Current                | I <sub>Q(V5V)</sub>        | EN = 0 V, $V5V = 5.25 V$ , mini-buck ON and no switching |      | 1.3 |      | mA   |

| V5V Non-switching<br>Current         | I <sub>I(V5V)</sub>        | EN = 5 V, V5V = 5.25 V, main-buck ON and no switching    |      | 2.8 |      | mA   |

| VIN Under-voltage                    | V <sub>IT(UVLO)</sub>      | VIN rising to release                                    | 4.25 |     | 4.5  | V    |

| Lock-out Threshold                   | V <sub>IT(UVLO,fall)</sub> | VIN falling to lock                                      |      |     | 4.1  |      |

| VIN Over-voltage Lock-               | V <sub>IT(OVLO)</sub>      | VIN rising to lock                                       |      | 42  |      | V    |

| out Threshold                        | V <sub>IT(OVLO,fall)</sub> | VIN falling to unlock                                    |      | 39  |      | ĺ    |

| V5V Regulation                       | V <sub>O(V5V)</sub>        | V5V error comparator threshold                           | 4.8  | 5.0 | 5.2  | V    |

| V5V PG Threshold                     | V <sub>IT(V5V)</sub>       | V5V rising                                               | 4.25 |     |      | V    |

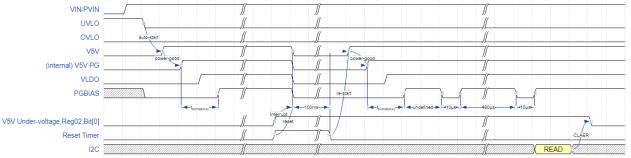

| V5V Under-voltage                    | V <sub>UVP(V5V)</sub>      | V5V falling                                              | 3.95 |     | 4.15 | V    |

| V5V Over-voltage                     | V <sub>OVP(V5V)</sub>      | V5V rising                                               |      | 5.9 |      | V    |

| VLDO Regulation                      | V <sub>O(VLDO)</sub>       | I <sub>VLOD</sub> = 10mA Reg0D[5:0] = 0x30               | 3.14 | 3.3 | 3.47 | V    |

| VLDO Under-voltage                   | V <sub>UVP(VLDO)</sub>     | Reg0D[5:0] = 0x30                                        | 2.9  |     |      | V    |

| PGBIAS Output Voltage                | V <sub>OL(PGBIAS)</sub>    | PGBIAS at logic-L, 1 mA Current into PGBIAS pin          |      |     | 0.3  | V    |

| Mini-buck Over-current               | I <sub>OCP(V5V)</sub>      |                                                          | 360  |     |      | mA   |

| VLDO Over-current                    | I <sub>OCP(VLDO)</sub>     |                                                          | 20   |     |      | mA   |

| Thermal Protection                   | T <sub>SD(HARD)</sub>      | Hard TSD, temperature rising                             |      | 155 |      | °C   |

|                                      | T <sub>SD(SOFT)</sub>      | Soft TSD, temperature rising                             |      | 145 |      |      |

|                                      | T <sub>SD(OFF)</sub>       | TSD release, temperature falling                         |      | 135 |      |      |

| SIGNAL PINS                          |                            |                                                          |      |     |      |      |

| Signal Pin Input Current             | I <sub>I(FB_VO)</sub>      | 5 V target (DACOUT[10:0] = 0x190)                        |      | 6   |      | μA   |

|                                      | I <sub>I(CSN)</sub>        |                                                          |      | 6   |      | μA   |

|                                      | I <sub>I(SYNC)</sub>       |                                                          |      |     | 1    | μA   |

| Signal Pin Output<br>Current         | I <sub>O(ADDR)</sub>       | $R_{ADDR} = 50 \text{ k}\Omega$ while PGBIAS=L           |      | 20  |      | μA   |

| Signal Pin Output<br>Voltage         | V <sub>O(FREQ)</sub>       | R <sub>FREQ</sub> = 40 kΩ                                |      | 1.2 |      | V    |

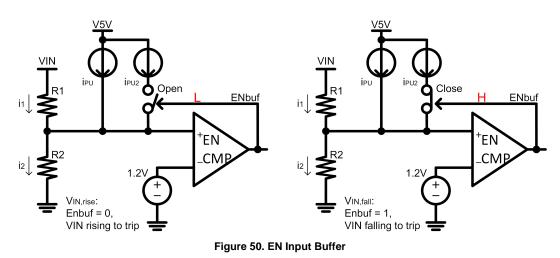

| EN Threshold                         | V <sub>IT(EN)</sub>        |                                                          | 1.15 |     | 1.25 | V    |

| EN Pin Pull-up Current               | I <sub>O(EN,rise)</sub>    | V <sub>EN</sub> < V <sub>IT(EN)</sub>                    |      | 1   |      | μA   |

|                                      | I <sub>O(EN,fall)</sub>    | $V_{EN} > V_{IT(EN)}$                                    |      | 2   |      |      |

## QOrvo

#### ACT4751 USB Fast Charger Power IC with 40V Input Voltage, 4A, Programmable Output Voltage and Current

| PARAMETER                                    | SYMBOL                          | TEST CONDITION                                                                                                   | MIN   | ТҮР    | MAX   | UNIT |

|----------------------------------------------|---------------------------------|------------------------------------------------------------------------------------------------------------------|-------|--------|-------|------|

| SYNC Pin Input<br>Threshold                  | V <sub>IT(SYNC)</sub>           | SYNC pin in slave                                                                                                | 0.55  |        | 1.4   | V    |

| SYNC Pin Output                              | V <sub>OH(SYNC)</sub>           | SYNC pin in master, outputs logic-H                                                                              | 3.2   |        | V5V   | V    |

| Voltage                                      | V <sub>OL(SYNC)</sub>           | SYNC pin in master, outputs logic-L                                                                              | 0     |        | 0.8   |      |

| I <sup>2</sup> C PINS                        |                                 |                                                                                                                  |       |        |       |      |

| Input Threshold                              | V <sub>IT(I<sup>2</sup>C)</sub> | SDA and SCL pins                                                                                                 | 0.55  |        | 1.25  | V    |

| Leakage Current                              | I <sub>LK(SDA)</sub>            | V <sub>SDA</sub> = 5 V                                                                                           |       |        | 1     | μA   |

| Output Voltage                               | V <sub>OL(SDA)</sub>            | 5 mA Current into SDA pin                                                                                        |       |        | 0.35  | V    |

| Input Capacitance                            | C <sub>I(I<sup>2</sup>C)</sub>  | SDA and SCL pins                                                                                                 |       |        | 10    | pF   |

| MAIN-BUCK REGULATO                           | OR                              |                                                                                                                  |       |        |       |      |

| DACOUT Accuracy                              | V <sub>DACOUT(24)</sub>         | 24 V target (DACOUT[10:0] = 0x780), 50 μA<br>current DACOUT sourcing                                             | -0.5% | 3.0    | +0.5% | V    |

|                                              | V <sub>DACOUT(5)</sub>          | 5 V target (DACOUT[10:0] = 0x190), 50 μA<br>current DACOUT sourcing                                              | -0.5% | 0.625  | +0.5% |      |

|                                              | ΔV <sub>DACOUT</sub>            | V <sub>DACOUT</sub> (n+1) - V <sub>DACOUT</sub> (n)                                                              | 0     | 1.5625 |       | mV   |

| FB_VO Accuracy                               | Vo                              | W.r.t. V <sub>REFIN</sub> , V <sub>REFIN</sub> = 3 V                                                             | -1%   | 24     | 1%    | V    |

| Output Current Limit<br>Programming Accuracy | I <sub>LIM(100)</sub>           | 100% target (ILIM[7:0] = 0xFF)                                                                                   | 98.5  |        | 101.5 | μA   |

|                                              | I <sub>LIM(25)</sub>            | 25% target (ILIM[7:0] = 0x3F)                                                                                    | 24.25 |        | 25.75 |      |

|                                              | ΔI <sub>LIM</sub>               | I <sub>LIM</sub> (n+1) - I <sub>LIM</sub> (n)                                                                    | 0     | 0.4    |       |      |

| Constant Current<br>Operation Programming    | V <sub>CCMODE(100)</sub>        | Differential voltage (V <sub>FB_VO</sub> - V <sub>CSN</sub> ) at V <sub>LIM</sub> = 1.6 V                        | 78.5  |        | 81.5  | mV   |

| Accuracy                                     | V <sub>CCMODE(25)</sub>         | Differential voltage (V <sub>FB_VO</sub> - V <sub>CSN</sub> ) at V <sub>LIM</sub> = 0.4 V                        | 19.3  |        | 20.7  |      |

| PG Output Voltage                            | V <sub>OL(PG)</sub>             | PG at logic-L, 1 mA Current into PG pin                                                                          |       |        | 0.3   | V    |

| PG Threshold Upper<br>Limit <sup>[1]</sup>   | V <sub>IH(VO)</sub>             | Threshold of Reg03[2], VO_FB w.r.t. $V_{REFIN}$ , $V_{REFIN} = 3 V$                                              | +5%   |        | +8%   |      |

| PG Threshold Lower<br>Limit <sup>[1]</sup>   | V <sub>IL(VO)</sub>             | Threshold of Reg03[2], VO_FB w.r.t. V <sub>REFIN</sub> ,<br>V <sub>REFIN</sub> = 3 V                             | -8%   |        | -5%   |      |

| FB_VO<br>Over-voltage                        | V <sub>OVP</sub>                | VO_FB w.r.t. V <sub>REFIN</sub> , V <sub>REFIN</sub> = 3 V                                                       | +8%   |        |       | V    |

| FB_VO<br>Under-voltage <sup>[2]</sup>        | V <sub>UVP(CC)</sub>            | $\frac{\text{Reg0B[3]} = \text{logic-L, VO_FB w.r.t. V}_{\text{REFIN}},}{\text{V}_{\text{REFIN}} = 3 \text{ V}}$ |       | 2.7    | 2.76  | V    |

|                                              | V <sub>UVP(CV)</sub>            | Reg0B[3] = logic-H, VO_FB w.r.t. V <sub>REFIN</sub> ,<br>V <sub>REFIN</sub> = 3 V                                |       |        | -8%   |      |

| FB_VO<br>Constant Current                    | V <sub>IT(CC,rise)</sub>        | Enable CC loop, Reg09[3] = logic-H, VO_FB rising                                                                 |       | 2.3    | 2.5   | V    |

| Activation Threshold                         | V <sub>IT(CC,fall)</sub>        | Disable CC loop, Reg09[3] = logic-H, VO_FB<br>falling                                                            |       | 2.2    |       |      |

| Main-buck Cycle-by-                          | I <sub>OCP(CBC,high)</sub>      | High-side FET limit to trigger                                                                                   | 5.5   | İ      |       | Α    |

| cycle Current Limit                          | I <sub>OCP(CBC,low)</sub>       | Low-side FET limit to release                                                                                    |       | 4.2    |       |      |

#### ACT4751 USB Fast Charger Power IC with 40V Input Voltage, 4A, Programmable **Output Voltage and Current**

| PARAMETER            | SYMBOL           | TEST CONDITION | MIN | ΤΥΡ | MAX | UNIT |

|----------------------|------------------|----------------|-----|-----|-----|------|

| Discharge Resistance | R <sub>DIS</sub> |                |     | 1.2 |     | kΩ   |

[1] See Main-buck Power-Good for details.

[2] See Under-Voltage Protection for details.

#### **Timing Requirements**

| PARAMETER                  | SYMBOL                 | CONDITION                                                                              | MIN  | TYP | MAX  | UNIT     |

|----------------------------|------------------------|----------------------------------------------------------------------------------------|------|-----|------|----------|

| I <sup>2</sup> C BLOCK     | 1                      |                                                                                        | !    |     |      | <u>.</u> |

| SCL Clock Frequency        | f <sub>SCL</sub>       | (no internal time out)                                                                 | 0    |     | 1000 | kHz      |

| SCL Pulse Width            | t <sub>LOW(SCL)</sub>  | Logic-L level                                                                          | 0.5  |     |      | μs       |

|                            | t <sub>HIGH(SCL)</sub> | Logic-H level                                                                          | 0.26 |     | 1    |          |

| SDA Set-up Time            | t <sub>SU(SDA)</sub>   |                                                                                        | 50   |     |      | ns       |

| SDA Hold Time              | t <sub>H(SDA)</sub>    |                                                                                        | 0    |     |      | ns       |

| START Set-up Time          | t <sub>SU(START)</sub> |                                                                                        | 260  |     | 1    | ns       |

| STOP Set-up Time           | t <sub>SU(STOP)</sub>  |                                                                                        | 260  |     |      | ns       |

| EN pin INPUT               | -                      |                                                                                        |      |     |      |          |

| EN Pulse Width             | t <sub>LOW(EN)</sub>   | Logic-L level                                                                          | 30   |     |      | μs       |

| SYNC pin INPUT             | -                      |                                                                                        | !    |     |      |          |

| SYNC Frequency<br>Range    | f <sub>SYNC</sub>      | $20k\Omega < R_{ADDR} < 50k\Omega$                                                     | 400  |     | 2500 | kHz      |

| SYNC Frequency<br>Accuracy |                        | $20k\Omega < R_{ADDR} < 50k\Omega$ , referring to the frequency setpoint by $R_{FREQ}$ | 75%  |     | 125% |          |

| SYNC Input Duty            | D <sub>IN(SYNC)</sub>  | $20k\Omega < R_{ADDR} < 50k\Omega$                                                     | 40%  |     | 60%  |          |

#### **Switching Characteristics**

PVIN = VIN = 12 V, V5V = 5 V (external supply), EN = 5 V,  $T_A = 25^{\circ}C$ , unless otherwise specified

| PARAMETER                                                       | SYMBOL                   | TEST CONDITION                                               | MIN | ТҮР | MAX | UNIT  |

|-----------------------------------------------------------------|--------------------------|--------------------------------------------------------------|-----|-----|-----|-------|

| BIAS BLOCK                                                      |                          |                                                              |     |     |     | ,     |

| Mini-Buck Switching<br>Frequency                                | f <sub>SW(V5V)</sub>     |                                                              | 2.0 |     |     | MHz   |

| Mini-Buck Spread-<br>Spectrum Dithering<br>Range <sup>[1]</sup> | f <sub>SPSP(V5V)</sub>   | Frequency modulation range w.r.t. f <sub>SW(V5V)</sub> value |     | ±7% |     |       |

| Mini-Buck Spread-<br>Spectrum Cycle                             | N <sub>SPSP(V5V)</sub>   | Number of T <sub>ON</sub> cycles                             |     | 32  |     | cycle |

| Mini-Buck Soft-Start<br>Time                                    | t <sub>SS(V5V)</sub>     | "VIN = $V_{IT(UVLO)}$ " to "V5V = $V_{IT(V5V)}$ "            |     | 0.5 |     | ms    |

| Mini-Buck UVP Mask<br>Timer                                     | t <sub>D(V5V,mask)</sub> |                                                              |     | 1   |     | ms    |

| Wait Timer before Error<br>Reset                                | t <sub>D(RESET)</sub>    |                                                              |     | 100 |     | ms    |

## QOCVO.

#### ACT4751 USB Fast Charger Power IC with 40V Input Voltage, 4A, Programmable **Output Voltage and Current**

| PARAMETER                                                       | RAMETER SYMBOL TEST CONDITION |                                                                            | MIN  | TYP  | MAX | UNIT  |  |

|-----------------------------------------------------------------|-------------------------------|----------------------------------------------------------------------------|------|------|-----|-------|--|

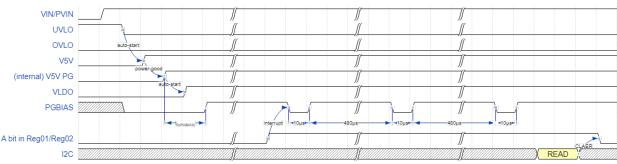

| PGBIAS Delay                                                    | t <sub>D(PGBIAS)</sub>        | "V5V = V <sub>IT(V5V)</sub> " to PGBIAS↑, target 3 ms<br>(Reg08[4:3] = 11) | -10% | 3    | 10% | ms    |  |

| AUX LDO Soft-Start<br>Time <sup>[2]</sup>                       | t <sub>SS(LDO)</sub>          | Just for reference, Reg0D[5:0] = 0x31                                      |      | 100  |     | μs    |  |

| I <sup>2</sup> C BLOCK                                          |                               |                                                                            |      |      |     | ,     |  |

| SDA Fall Time                                                   | t <sub>F(SDA)</sub>           | Pull-up to 5-V source via 10 k $\Omega$                                    |      |      | 120 | ns    |  |

| MAIN-BUCK REGULAT                                               | OR                            |                                                                            |      |      |     | ,     |  |

| Main-Buck Switching                                             | f <sub>SW(MAIN)(min)</sub>    | R <sub>FREQ</sub> = 200 kΩ                                                 | 400  | 450  | 500 | kHz   |  |

| Frequency                                                       | f <sub>SW(MAIN)(max)</sub>    | $R_{FREQ} = 40 \text{ k}\Omega$                                            | 2.0  | 2.25 | 2.5 | MHz   |  |

| SYNC Output Duty<br>Cycle                                       | D <sub>OUT(SYNC)</sub>        |                                                                            |      | 50%  |     |       |  |

| SYNC Input WDT Error                                            | $\Delta f_{SYNC(low)}$        | $20k\Omega < R_{ADDR} < 50k\Omega$ , referring to the                      | 1    |      | 40% |       |  |

| Detection                                                       | $\Delta f_{SYNC(high)}$       | frequency setpoint by R <sub>FREQ</sub>                                    | 210% |      |     |       |  |

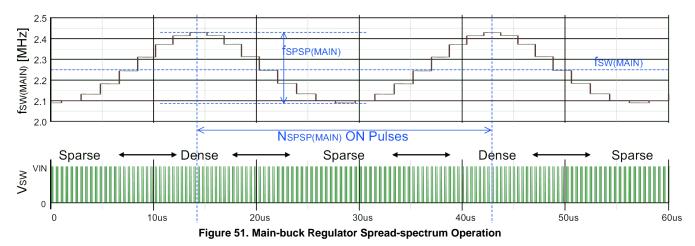

| Main-Buck Spread-<br>Spectrum Dithering<br>Range <sup>[1]</sup> | f <sub>SPSP(MAIN)</sub>       | Frequency modulation range w.r.t. f <sub>SW(MAIN)</sub>                    |      | ±7%  |     |       |  |

| Main-Buck Spread-<br>Spectrum Cycle                             | N <sub>SPSP(MAIN)</sub>       | Number of T <sub>ON</sub> cycles                                           |      | 64   |     | cycle |  |

| ON Time Control                                                 | t <sub>ON(min)</sub>          |                                                                            |      | 65   | 80  | ns    |  |

| OFF Time Control                                                | t <sub>OFF(min)</sub>         |                                                                            |      | 65   | 80  | ns    |  |

| Main-Buck Digital Servo<br>Clock Period                         | t <sub>W(SERVO)</sub>         |                                                                            |      | 8    |     | μs    |  |

| Hiccup Timer                                                    | t <sub>W(HICCUP)</sub>        |                                                                            |      | 100  |     | ms    |  |

| PG Delay                                                        | t <sub>D(PG)(min)</sub>       | FB_VO > V <sub>IL(VO)</sub> , 0 ms target (Reg08[7:6] = 00)                |      |      | 10  | μs    |  |

|                                                                 | t <sub>D(PG)(max)</sub>       | FB_VO > V <sub>IL(VO)</sub> , 4 ms target (Reg08[7:6] = 11)                | -10% | 4    | 10% | ms    |  |

<sup>[1]</sup> No production test <sup>[2]</sup> Not actively controlled, application board dependent

## QOCVO

#### ACT4751 USB Fast Charger Power IC with 40V Input Voltage, 4A, Programmable Output Voltage and Current

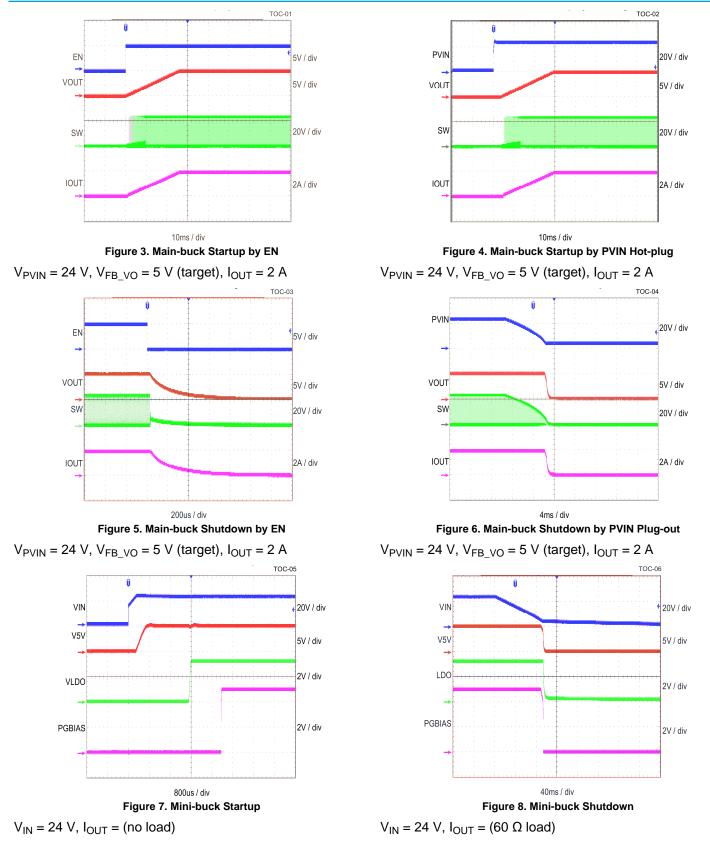

## **Typical Characteristic Curves**

## QOCVO

### ACT4751 USB Fast Charger Power IC with 40V Input Voltage, 4A, Programmable Output Voltage and Current

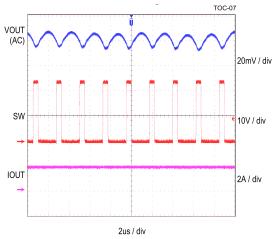

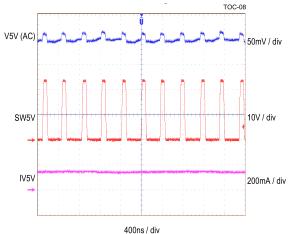

Figure 9. Main-buck Switching Waveform

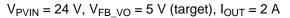

Figure 11. Main-buck Over Current Protection

$V_{IN} = 24 V$

Figure 10. Mini-buck Switching Waveform

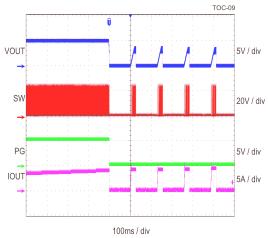

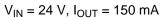

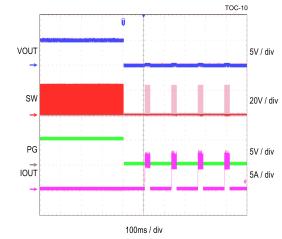

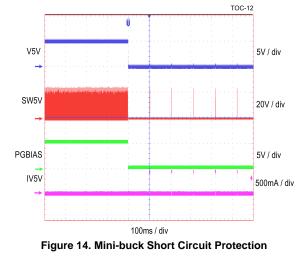

Figure 12. Main-buck Short Circuit Protection

$V_{PVIN} = 24 V, V_{FB_VO} = 5 V (target)$

$V_{IN} = 24 V$

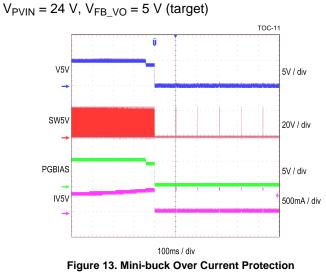

### ACT4751 USB Fast Charger Power IC with 40V Input Voltage, 4A, Programmable Output Voltage and Current

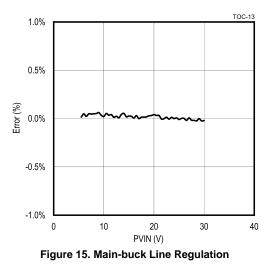

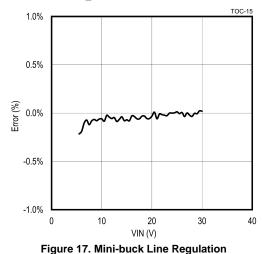

$V_{PVIN}$  = 4 to 30 V,  $V_{FB_VO}$  = 5 V (target),  $I_{OUT}$  = 2 A

$V_{PVIN} = 24 \text{ V}, V_{FB_VO} = 5 \text{ V} \text{ (target)}, I_{OUT} = 0.4 \text{ to } 3.6 \text{ A}$

$V_{PVIN} = 24 \text{ V}, V_{FB VO} = 5 \text{ V}$  (target),  $I_{OUT} = 0 \text{ to } 4 \text{ A}$

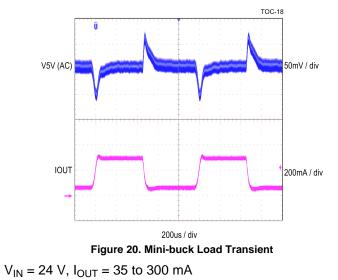

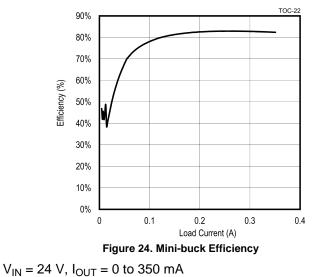

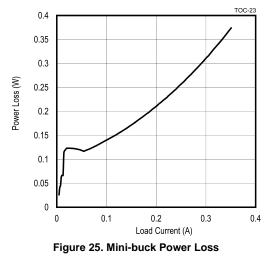

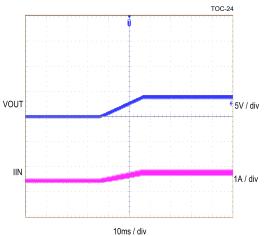

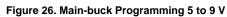

$V_{IN} = 24 \text{ V}, I_{OUT} = 0 \text{ to } 350 \text{ mA}$

### ACT4751 USB Fast Charger Power IC with 40V Input Voltage, 4A, Programmable Output Voltage and Current

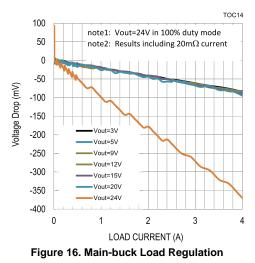

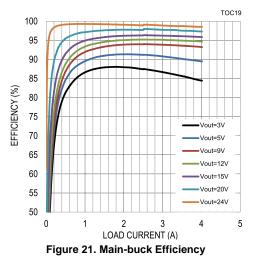

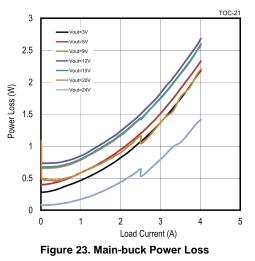

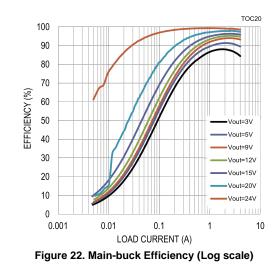

$V_{\text{PVIN}}$  = 24 V,  $V_{\text{FB}\_\text{VO}}$  = 3,5,9,12,15,20,24 V (target),  $I_{\text{OUT}}$  = 0 to 4 A

$V_{PVIN}$  = 24 V,  $V_{FB\_VO}$  = 3,5,9,12,15,20,24 V (target),  $I_{OUT}$  = 0 to 4 A

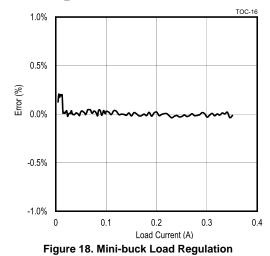

$V_{\mathsf{PVIN}}$  = 24 V,  $V_{\mathsf{FB}\_\mathsf{VO}}$  = 3,5,9,12,15,20,24 V (target),  $\mathsf{I}_{\mathsf{OUT}}$  = 0 to 4 A

#### ACT4751 USB Fast Charger Power IC with 40V Input Voltage, 4A, Programmable Output Voltage and Current

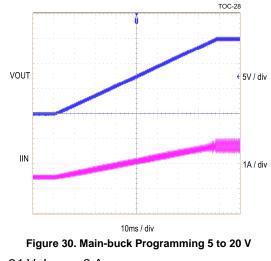

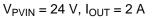

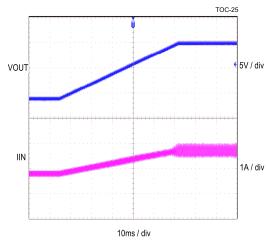

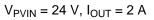

$V_{PVIN} = 24 V, I_{OUT} = 2 A$

$V_{PVIN} = 24 V, I_{OUT} = 2 A$

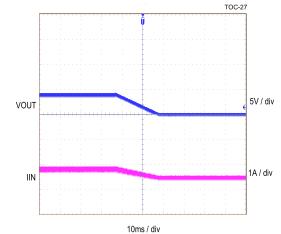

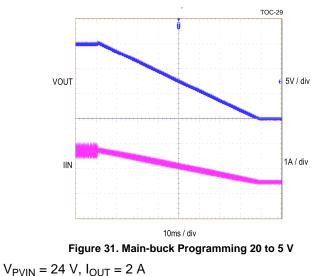

Figure 27. Main-buck Programming 9 to 20 V

Figure 29. Main-buck Programming 9 to 5 V

$V_{PVIN} = 24 V, I_{OUT} = 2 A$

### ACT4751 USB Fast Charger Power IC with 40V Input Voltage, 4A, Programmable Output Voltage and Current

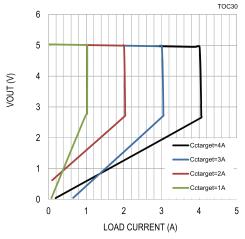

Figure 32. Main-buck Constant Current

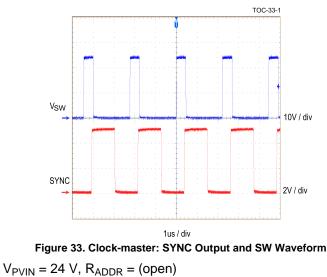

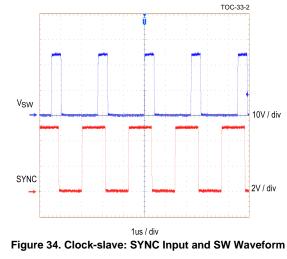

$V_{PVIN} = 24 \text{ V}, \text{ R}_{ADDR} = 50 \text{ k}\Omega$

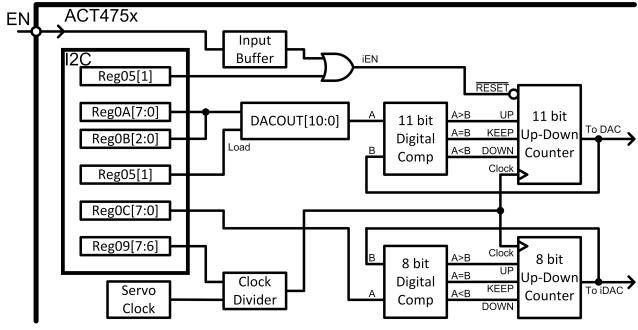

## I<sup>2</sup>C Registers

In this section, I<sup>2</sup>C register mappings and bit assignments are explained. Please refer to I<sup>2</sup>C Interface section how to access, how to setup these registers.

#### **Register Address Map**

This is an entire mapping of I<sup>2</sup>C registers on the ACT4751 device. Here are the meanings of each column in Table 1.

| Reg Addr    | I <sup>2</sup> C register address number in hexadecimal                                                                                       |  |  |  |  |  |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Reg Name    | Register name                                                                                                                                 |  |  |  |  |  |

| R/W         | Read / Write type of register<br><b>R</b> : Read only<br><b>W</b> : Write only<br><b>R/W</b> : Read and Write                                 |  |  |  |  |  |

| Def         | Default value                                                                                                                                 |  |  |  |  |  |

| F/P         | Factory Programming support<br>Y: The default values can be programmed by a production test.<br>N: The default values are fixed / hard-coded. |  |  |  |  |  |

| Description | Description of the register                                                                                                                   |  |  |  |  |  |

$\wedge$

Please contact your local sales representatives for availabilities of different **Factory Programming** default settings. See **Factory Programming Options**.

In Table 1 below, each register address value string is a link to the detailed bit description.

#### Table 1. Register Address Map

| Reg<br>Addr | Reg Name                           | R/W | Def  | F/P | Description                                                                  |

|-------------|------------------------------------|-----|------|-----|------------------------------------------------------------------------------|

| 0x00        | State-Machine                      | R   | —    | N   | Current position of the state-machine                                        |

| 0x01        | Interrupt #1                       | R   | —    | N   | Interrupt byte #1                                                            |

| 0x02        | Interrupt #2                       | R   | —    | N   | Interrupt byte #2                                                            |

| 0x03        | Status Flag                        | R   | —    | N   | Status byte (no interrupt)                                                   |

| 0x04        | (Reserved)                         | R   | —    | N   | (not in use)                                                                 |

| 0x05        | Command                            | R/W | 0x00 | N   | Command to trigger actions                                                   |

| 0x06        | Interrupt Mask #1                  | R/W | 0x00 | Y   | Interrupt mask byte #1 for the register Reg01                                |

| 0x07        | Interrupt Mask #2                  | R/W | 0x00 | Y   | Interrupt mask byte #2 for the register Reg02                                |

| 0x08        | Configuration byte #1              | R/W | 0x28 | Y   | Configure various device behaviors #1                                        |

| 0x09        | Configuration byte #2              | R/W | 0xF3 | Y   | Configure various device behaviors #2                                        |

| 0x0A        | DACOUT[10:3]                       | R/W | 0x32 | Y   | DACOUT programming value bit 10 to 3                                         |

| 0x0B        | DACOUT[2:0], Configuration byte #3 | R/W | 0x10 | Y   | DACOUT programming value bit 2 to 0<br>Configure various device behaviors #3 |

| 0x0C        | ILIM Value                         | R/W | 0xFF | Y   | ILIM programming value bit 7 to 0                                            |

| 0x0D        | AUX LDO Value                      | R/W | 0x30 | Y   | VLDO programming value bit 5 to 0                                            |

| 0x0E        | Configuration byte #4              | R/W | 0x23 | Y   | Configure various device behaviors #4                                        |

| 0x0F        | Configuration byte #5              | R/W | 0x9E | Y   | Configure various device behaviors #5                                        |

## QOLVO

#### **Register Bit Maps**

Following sub-sections explain bit assignments of each I<sup>2</sup>C register. Here are the meanings of each column in below bit tables.

| Bit #       | Bit position (number)            |

|-------------|----------------------------------|

| Bit(s) Name | Bit(s) name                      |

| Def         | Default value                    |

| Description | <b>Description</b> of the bit(s) |

#### **0x00 State-Machine**

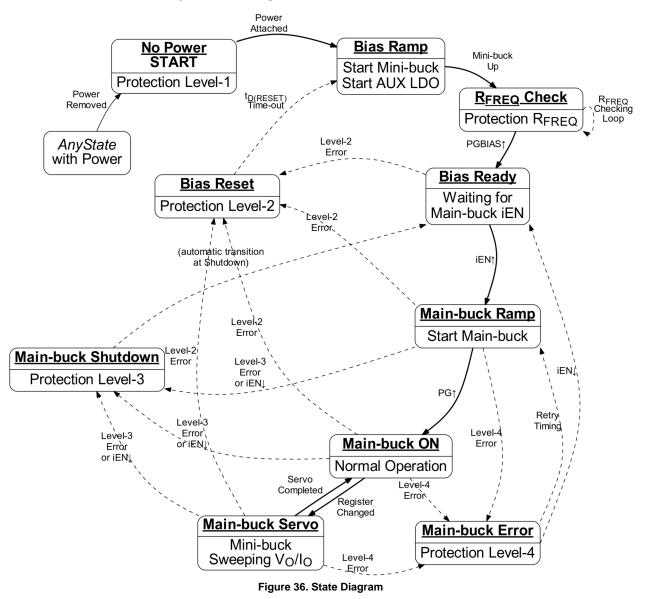

The register 0x00 is **Read Only** type. It indicates current position of the state-machine. See Control Logic.

#### Table 2. Register 0x00

| Bit # | Bit(s) Name | Def | Description   |

|-------|-------------|-----|---------------|

| 7     |             | 0   | (un-used bit) |

| 6     |             | 0   | (un-used bit) |

| 5     |             | 0   | (un-used bit) |

| 4     |             | 0   | (un-used bit) |

| 3     | State[3]    | 0   | See Table 3.  |

| 2     | State[2]    | 0   |               |

| 1     | State[1]    | 0   |               |

| 0     | State[0]    | 0   |               |

#### Table 3. State-Machine Bits [3:0]

| Value (bin) | Value (hex) | Position of State-Machine                            |

|-------------|-------------|------------------------------------------------------|

| 0000        | 0x00        | No Power, in Under-Voltage Lock-Out                  |

| 0001        | 0x01        | Bias Ramp, initialing mini-buck <sup>[1]</sup>       |

| 0010        | 0x02        | Bias Reset                                           |

| 0011        | 0x03        | Bias Ramp checking R <sub>ADDR</sub> <sup>[1]</sup>  |

| 0100        | 0x04        | Bias Ramp                                            |

| 0101        | 0x05        | Bias Ready checking R <sub>FREQ</sub> <sup>[1]</sup> |

| 0110        | 0x06        | R <sub>FREQ</sub> Checking Loop <sup>[2]</sup>       |

| 0111        | 0x07        | Bias Ready                                           |

| 1000        | 0x08        | Main-buck Ramp enabling main-buck <sup>[1]</sup>     |

| 1001        | 0x09        | Main-buck Ramp                                       |

| 1010        | 0x0A        | Main-buck ON                                         |

| 1011        | 0x0B        | Main-buck Shutdown                                   |

| 1100        | 0x0C        | Main-buck Error                                      |

<sup>[1]</sup> Short transit, not staying loner at this position <sup>[2]</sup> Not in the Table 27, see R<sub>FREQ</sub> Checking Loop

#### 0x01: Interrupt #1

#### 0x02: Interrupt #2

The registers 0x01 and 0x02 are **Read Only**. These 2 registers indicate cause(s) of the latest interrupt event by setting **1** at corresponding bit(s), so bit(s) of **0** mean nothing happened (normal). In the Reg01 and Reg02, trigger events setting **1** are described. See Interrupt Output.

Bits in these registers will be automatically cleared by reading the value with an I<sup>2</sup>C command.

This automatic bit-clear action applies if the cause of an interrupt is resolved at the timing of a READ action. For most of the bits in 0x01 and 0x02, the automatic bit-clear happens because these protection events trigger shutdown actions to resolve the error situation.

#### Table 4. Register 0x01

| Bit # | Bit(s) Name                     | Def | Description                                                                                                         |

|-------|---------------------------------|-----|---------------------------------------------------------------------------------------------------------------------|

| 7     | Main-buck in CC/CV              | 0   | Becomes 1 when the main-buck transits $CC \Rightarrow CV$ or $CV \Rightarrow CC$ . See $CC / CV$ Interrupt/Monitor. |

| 6     |                                 | 0   | (un-used bit)                                                                                                       |

| 5     | Out of Range, SYNC Input        | 0   | Becomes <b>1</b> when the SYNC pin input clock is out of range. See Clock Synchronizer.                             |

| 4     | Out of Range, R <sub>FREQ</sub> | 0   | Becomes <b>1</b> when the $R_{FREQ}$ value, probed, is out of range. See $R_{FREQ}$ Protection.                     |

| 3     | T <sub>SD(HARD)</sub> Event     | 0   | Becomes 1 when the $T_J$ exceeds the $T_{\text{SD}(\text{HARD})}$ threshold. See Thermal Protection.                |

| 2     | T <sub>SD(SOFT)</sub> Event     | 0   | Becomes <b>1</b> when the $T_J$ exceeds the $T_{SD(SOFT)}$ threshold. See Thermal Protection.                       |

| 1     |                                 | 0   | (un-used bit)                                                                                                       |

| 0     | V <sub>IT(OVLO)</sub> Event     | 0   | Becomes 1 when the $V_{\text{PVIN}}$ exceeds the $V_{\text{IT}(\text{OVLO})}$ threshold. See Over-Voltage Lock-Out. |

#### Table 5. Register 0x02

| Bit # | Bit(s) Name                                        | Def | Description                                                                                                                     |

|-------|----------------------------------------------------|-----|---------------------------------------------------------------------------------------------------------------------------------|

| 7     |                                                    | 0   | (un-used bit)                                                                                                                   |

| 6     | Main-buck Over-current Event                       | 0   | Becomes <b>1</b> when the output current in Over-Current Protection.                                                            |

| 5     | V <sub>OVP</sub> Event                             | 0   | Becomes 1 when the $V_{O}$ exceeds the $V_{OVP}$ threshold. See Over-Voltage Protection                                         |

| 4     | V <sub>UVP(CV)</sub> or V <sub>UVP(CC)</sub> Event | 0   | Becomes 1 when the $V_O$ falls below the $V_{UVP(CV)}$ or $V_{UVP(CC)}$ threshold. See Under-Voltage Protection.                |

| 3     | AUX LDO Under-voltage                              | 0   | Becomes 1 when the $V_{O(VLDO)}$ falls below the $V_{UVP(VLDO)}$ threshold. See AUX LDO Under-Voltage Protection                |

| 2     | I <sub>OCP(V5V)</sub> Event                        | 0   | Becomes 1 when the output current of the mini-buck exceeds the $I_{OCP(V5V)}$ threshold. See Mini-buck Over-Current Protection. |

| 1     | V <sub>OVP(V5V)</sub> Event                        | 0   | Becomes 1 when the $V_{O(V5V)}$ exceeds the $V_{OVP(V5V)}$ threshold. See Mini-buck Over-Voltage Protection.                    |

| 0     | V <sub>UVP(V5V)</sub> Event                        | 0   | Becomes 1 when the $V_{O(V5V)}$ falls below the $V_{UVP(V5V)}$ threshold.<br>See Mini-buck Under-Voltage Protection.            |

#### **0x03: Status Flag**

The register 0x03 is **Read Only** type. It indicates various status flags from internal circuit blocks.

#### Table 6. Register 0x03

| Bit # | Bit(s) Name       | Def | Description                                                                                                                                               |

|-------|-------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7     | WDT High          | 0   | 1*: Clock input at SYNC is too high/low to accept.                                                                                                        |

| 6     | WDT Low           | 0   | <b>0</b> : (normal), See SYNC Input Watch Dog Timer.                                                                                                      |

| 5     | Mini-buck in 100% | 0   | <ul><li>1*: Mini-buck is operating in 100% mode.</li><li>0: Mini-buck is operating out of 100% mode.</li><li>See Mini-buck 100% Duty Operation.</li></ul> |

| 4     | Main-buck in CC   | 0   | <ul><li>1*: Main-buck is operating in CC mode.</li><li>0: Main-buck is operating in CV mode.</li><li>See Programmable Current Limit.</li></ul>            |

| 3     | Main-buck in 100% | 0   | <ul><li>1*: Main-buck is operating in 100% mode.</li><li>0: Main-buck is operating out of 100% mode.</li><li>See 100% Duty Operation.</li></ul>           |

| 2     | PG of Main-buck   | 0   | 1*: Main-buck in "Power-good" condition<br><b>0</b> : Main-buck in <b>NOT</b> "Power-good" condition<br>See Main-buck Power-Good.                         |

| 1     |                   | 0   | (un-used bit)                                                                                                                                             |

| 0     |                   | 0   | (un-used bit)                                                                                                                                             |

#### 0x04: (Reserved)

The register 0x04 is reserved for future spins. Nothing is assigned to this register.

#### 0x05: Command

The register 0x05 is Read / Write type. A writing action to this register triggers a certain action at the device.

#### Table 7. Register 0x05

| Bit # | Bit(s) Name      | Def | Description                                                                                               |

|-------|------------------|-----|-----------------------------------------------------------------------------------------------------------|

| 7     |                  | 0   | (un-used bit)                                                                                             |

| 6     |                  | 0   | (un-used bit)                                                                                             |

| 5     |                  | 0   | (un-used bit)                                                                                             |

| 4     |                  | 0   | (un-used bit)                                                                                             |

| 3     |                  | 0   | (un-used bit)                                                                                             |

| 2     |                  | 0   | (un-used bit)                                                                                             |

| 1     | Load DACOUT      | 0   | Setting <b>1</b> to load DACOUT value in effect.<br>Always reads <b>0</b> . See Loading New DACOUT Value. |

| 0     | Enable Main-buck | 0   | Writing 1 to enable Main-buck<br>See Main-buck Enable Control                                             |

#### 0x06: Interrupt Mask #1

#### 0x07: Interrupt Mask #2

The registers 0x06 and 0x07 are **Read / Write** type. These 2 registers are corresponding to the Reg01 and Reg02 respectively. Any **1** bit in Reg06 and Reg07 prevents (masks) an interrupt event triggered by the corresponding bit in Reg01 and Reg02. For example, Setting the Reg07[5] bit makes no interrupt event even though an over-voltage happened at the Reg02[5] bit. See Interrupt Output.

When the Reg08[5] "Mask All" bit is 1, all Reg06 and Reg07 bits are overridden to 1 internally regardless of register values there.

#### Table 8. Register 0x06

| Bit # | Bit(s) Name                          | Def | Description                                   |

|-------|--------------------------------------|-----|-----------------------------------------------|

| 7     | Mask Main-buck in CC/CV              | 0   | 1: mask bit 7 of Reg01<br><b>0:</b> (no-mask) |

| 6     |                                      | 0   | (un-used bit)                                 |

| 5     | Mask Out of Range, SYNC Input        | 0   | 1: mask bit 5 of Reg01<br><b>0:</b> (no-mask) |

| 4     | Mask Out of Range, R <sub>FREQ</sub> | 0   | 1: mask bit 4 of Reg01<br><b>0:</b> (no-mask) |

| 3     | Mask T <sub>SD(HARD)</sub> Event     | 0   | 1: mask bit 3 of Reg01<br>0: (no-mask)        |

| 2     | Mask T <sub>SD(SOFT)</sub> Event     | 0   | 1: mask bit 2 of Reg01<br>0: (no-mask)        |

| 1     |                                      | 0   | (un-used bit)                                 |

| 0     | Mask V <sub>IT(OVLO)</sub> Event     | 0   | 1: mask bit 0 of Reg01<br>0: (no-mask)        |

#### Table 9. Register 0x07

| Bit # | Bit(s) Name                               | Def | Description                            |

|-------|-------------------------------------------|-----|----------------------------------------|

| 7     |                                           | 0   | (un-used bit)                          |

| 6     | Mask Main-buck Over-current<br>Event      | 0   | 1: mask bit 6 of Reg02<br>0: (no-mask) |

| 5     | Mask V <sub>OVP</sub> Event               | 0   | 1: mask bit 5 of Reg02<br>0: (no-mask) |

| 4     | Mask $V_{UVP(CV)}$ or $V_{UVP(CC)}$ Event | 0   | 1: mask bit 4 of Reg02<br>0: (no-mask) |

| 3     | Mask AUX LDO Under-voltage                | 0   | 1: mask bit 3 of Reg02<br>0: (no-mask) |

| 2     | Mask I <sub>OCP(V5V)</sub> Event          | 0   | 1: mask bit 2 of Reg02<br>0: (no-mask) |

| 1     | Mask V <sub>OVP(V5V)</sub> Event          | 0   | 1: mask bit 1 of Reg02<br>0: (no-mask) |

| 0     | Mask V <sub>UVP(V5V)</sub> Event          | 0   | 1: mask bit 0 of Reg02<br>0: (no-mask) |

### 0x08: Configuration byte #1

The register 0x08 is Read / Write type. It configures the device behaviors as described.

#### Table 10. Register 0x08

| Bit # | Bit(s) Name     | Def | Description                                                                                                                  |  |

|-------|-----------------|-----|------------------------------------------------------------------------------------------------------------------------------|--|

| 7     | PG Delay[1]     | 0   | See Table 11.                                                                                                                |  |

| 6     | PG Delay[0]     | 0   | See Main-buck Power-Good.                                                                                                    |  |

| 5     | Mask All        | 1   | <ol> <li>overrides all Reg06 and Reg07 bits 1 internally.</li> <li>"masking" follows each bit of Reg06 and Reg07.</li> </ol> |  |

| 4     | PGBIAS Delay[1] | 0   | See Table 12 and                                                                                                             |  |

| 3     | PGBIAS Delay[0] | 1   | See PGBIAS Indicator Output.                                                                                                 |  |

| 2     |                 | 0   | (un-used bit)                                                                                                                |  |

| 1     |                 | 0   | (un-used bit)                                                                                                                |  |

| 0     |                 | 0   | (un-used bit)                                                                                                                |  |

Table 11. PG Delay [1:0]

| Value (bin) | Value (hex) | PG pin Delay Time |

|-------------|-------------|-------------------|

| 00          | 0x00        | 0 ms (default)    |

| 01          | 0x01        | 0.25 ms           |

| 10          | 0x02        | 1 ms              |

| 11          | 0x03        | 4 ms              |

Table 12. PGBIAS Delay [1:0]

| Value (bin) | Value (hex) | PGBIAS pin Delay Time |

|-------------|-------------|-----------------------|

| 00          | 0x00        | 1 ms                  |

| 01          | 0x01        | 1.25 ms (default)     |

| 10          | 0x02        | 1.5 ms                |

| 11          | 0x03        | 3 ms                  |

### 0x09: Configuration byte #2

The register 0x09 is Read / Write type. It configures the device behaviors as described.

#### Table 13. Register 0x09

| Bit # | Bit(s) Name        | Def | Description                                                                                                                                                                                                                                              |  |

|-------|--------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 7     | Servo Clock[1]     | 1   | See Table 14.                                                                                                                                                                                                                                            |  |

| 6     | Servo Clock[0]     | 1   |                                                                                                                                                                                                                                                          |  |

| 5     | Discharge in Servo | 1   | $\begin{array}{l} \textbf{1:} Use \mbox{ discharge resistor to drive } V_{O} \mbox{ servo down.} \\ 0: \mbox{ Not use discharge resistor in servo.} \\ See \mbox{ Negative Transition with } R_{DIS} \mbox{ and Output Discharge Resistor.} \end{array}$ |  |

| 4     | Discharge at OFF   | 1   | <ol> <li>Use discharge resistor when main-buck disabled.</li> <li>Not use discharge resistor when main-buck disabled.</li> <li>See Main-buck Enable Control and Output Discharge Resistor.</li> </ol>                                                    |  |

| 3     | Main-buck No UVP   | 0   | 1: disable main-buck under-voltage protection.<br><b>0:</b> use main-buck under-voltage protection.<br>See UVP selection.                                                                                                                                |  |

| 2     | Hiccup / Latch-off | 0   | 1: Latch-off action in main-buck.<br>0: Hiccup action in main-buck.<br>See Under-Voltage Hiccup and Under-Voltage Latch-off.<br>Also, see SYNC Error Hiccup and SYNC Error Latch-off.                                                                    |  |

| 1     | Enable Mini-buck   | 1   | <ul> <li>1: enable Mini-buck, automatically start-up Mini-buck.</li> <li>0: disable Mini-buck, manually start-up Mini-buck.</li> <li>See V5V, External 5V Supply.</li> </ul>                                                                             |  |

| 0     | Enable AUX LDO     | 1   | 1: enable AUX LDO, automatically start-up AUX LDO.<br>0: disable AUX LDO, manually start-up AUX LDO.<br>See AUX LDO Enable.                                                                                                                              |  |

#### Table 14. Servo Clock [1:0]

| Value (bin) | Value (hex) | Servo Clock Period                  |  |

|-------------|-------------|-------------------------------------|--|

| 00          | 0x00        | t <sub>W(SERVO)</sub> × 1           |  |

| 01          | 0x01        | t <sub>W(SERVO)</sub> × 2           |  |

| 10          | 0x02        | t <sub>W(SERVO)</sub> × 4           |  |

| 11          | 0x03        | t <sub>W(SERVO)</sub> × 8 (default) |  |

#### 0x0A: DACOUT Value [10:3]

The register 0x0A is Read / Write type. It programs DACOUT value.

#### Table 15. Register 0x0A

| Bit # | Bit(s) Name | Def | Description                                            |

|-------|-------------|-----|--------------------------------------------------------|

| 7     | DACOUT[10]  | 0   | See Table 16.                                          |

| 6     | DACOUT[9]   | 0   | 3 more bits in Reg0B.<br>See Output Voltage Reference. |

| 5     | DACOUT[8]   | 1   |                                                        |

| 4     | DACOUT[7]   | 1   |                                                        |

| 3     | DACOUT[6]   | 0   |                                                        |

| 2     | DACOUT[5]   | 0   |                                                        |

| 1     | DACOUT[4]   | 1   |                                                        |

| 0     | DACOUT[3]   | 0   |                                                        |

Table 16. DACOUT[10:0]

| Value (bin)   | Value (hex) | DACOUT Voltage (mV)   | V <sub>O</sub> Voltage (V) |  |

|---------------|-------------|-----------------------|----------------------------|--|

| 000 0000 0000 | 0x000       | 0.0                   | 0.0000                     |  |

|               |             |                       |                            |  |

| 000 1110 1111 | 0x0EF       | 373.4                 | 2.9875                     |  |

| 000 1111 0000 | 0x0F0       | 375.0 <sup>[1]</sup>  | 3.0000                     |  |

| 000 1111 0001 | 0x0F1       | 376.6                 | 3.0125                     |  |

|               |             |                       |                            |  |

| 001 0000 1000 | 0x108       | 412.5                 | 3.3                        |  |

|               |             |                       |                            |  |

| 001 1001 0000 | 0x190       | 625.0 (default)       | 5                          |  |

|               |             |                       |                            |  |

| 010 1101 0000 | 0x2D0       | 1125.0                | 9                          |  |

|               |             |                       |                            |  |

| 011 1100 0000 | 0x3C0       | 1500.0                | 12                         |  |

|               |             |                       |                            |  |

| 100 1011 0000 | 0x480       | 1875.0                | 15                         |  |

|               |             |                       |                            |  |

| 111 0111 1111 | 0x77F       | 2998.4                | 23.9875                    |  |

| 111 1000 0000 | 0x780       | 3000.0 <sup>[2]</sup> | 24.0000                    |  |

| 111 1000 0001 | 0x781       | 3000.0                | 24.0000                    |  |

|               |             |                       |                            |  |

| 111 1111 1111 | 0x7FF       | 3000.0                | 24.0000                    |  |

<sup>[1]</sup> Minimum value of the DACOUT range characterized. <sup>[2]</sup> Maximum value of the DACOUT range characterized.

#### ACT4751 USB Fast Charger Power IC with 40V Input Voltage, 4A, Programmable Output Voltage and Current

### 0x0B: Configuration byte #3, DACOUT[2:0]

The register 0x0B is **Read / Write** type. It configures the device behaviors as described.

#### Table 17. Register 0x0B

| Bit # | Bit(s) Name                          | Def | Description                                                                                                                                                      |  |

|-------|--------------------------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 7     | Enable main-buck 100%                | 0   | 1: enable main-buck 100% mode.<br><b>0:</b> disable main-buck 100% mode.<br>See 100% Duty Operation.                                                             |  |

| 6     | Enable main-buck Spread-<br>Spectrum | 0   | 1: enable main-buck spread-spectrum operation.<br>0: disable main-buck spread-spectrum operation.<br>See Spread-spectrum Operation.                              |  |

| 5     |                                      | 0   | (un-used bit)                                                                                                                                                    |  |

| 4     | Enable main-buck CC                  | 1   | <ol> <li>enable main-buck Constant-current operation.</li> <li>disable main-buck Constant-current operation.</li> <li>See Programmable Current Limit.</li> </ol> |  |

| 3     | Select main-buck UVP                 | 0   | 1: select $V_{UVP(CV)}$ .<br><b>0</b> : select $V_{UVP(CC)}$ .<br>See UVP selection.                                                                             |  |

| 2     | DACOUT[2]                            | 0   | See Table 16.                                                                                                                                                    |  |

| 1     | DACOUT[1]                            | 0   | 8 more bits in Reg0A.<br>See Output Voltage Reference.                                                                                                           |  |

| 0     | DACOUT[0]                            | 0   |                                                                                                                                                                  |  |

#### **0x0C: ILIM Value**

The register 0x0C is Read / Write type. It programs ILIM value.

#### Table 18. Register 0x0C

| Bit # | Bit(s) Name | Def | Description                   |

|-------|-------------|-----|-------------------------------|

| 7     | ILIM[7]     | 1   | See Table 19.                 |

| 6     | ILIM[6]     | 1   | See Output Current Reference. |

| 5     | ILIM[5]     | 1   |                               |

| 4     | ILIM[4]     | 1   |                               |

| 3     | ILIM[3]     | 1   |                               |

| 2     | ILIM[2]     | 1   |                               |

| 1     | ILIM[1]     | 1   |                               |

| 0     | ILIM[0]     | 1   |                               |

Table 19. ILIM[7:0]

| Value (bin) | Value (hex)                           | I <sub>LIM</sub> Current (μΑ)                 | Output Current (mA)<br>with R <sub>CS</sub> =20 mΩ<br>and R <sub>ILIM</sub> =16 kΩ |  |  |

|-------------|---------------------------------------|-----------------------------------------------|------------------------------------------------------------------------------------|--|--|

| 0000 0000   | 0x00                                  | 0.39                                          | 15.6                                                                               |  |  |

| 0000 0001   | 0x01                                  | 0.78                                          | 31.3                                                                               |  |  |

| 0000 0010   | 0x02                                  | 1.17                                          | 46.9                                                                               |  |  |

|             | · · · · · · · · · · · · · · · · · · · |                                               |                                                                                    |  |  |

| 1111 1101   | 0xFD                                  | 99.2                                          | 3969                                                                               |  |  |

| 1111 1110   | 0xFE                                  | 99.6                                          | 3984                                                                               |  |  |

| 1111 1111   | 0xFF                                  | 100.0 (default)<br>(= I <sub>LIM(100)</sub> ) | 4000                                                                               |  |  |

#### 0x0D: AUX LDO Value

The register 0x0D is **Read / Write** type. It programs AUX LDO value.

#### Table 20. Register 0x0D

| Bit # | Bit(s) Name    | Def | Description                             |

|-------|----------------|-----|-----------------------------------------|

| 7     |                | 0   | (un-used bit)                           |

| 6     |                | 0   | (un-used bit)                           |

| 5     | LDO Voltage[5] | 1   | See Table 21.                           |

| 4     | LDO Voltage[4] | 1   | See AUX LDO Output Voltage Programming. |

| 3     | LDO Voltage[3] | 0   |                                         |

| 2     | LDO Voltage[2] | 0   |                                         |

| 1     | LDO Voltage[1] | 0   |                                         |

| 0     | LDO Voltage[0] | 0   |                                         |

Table 21. LDO Voltage[5:0]

| Value (bin) | Value (hex) | V <sub>O(VLDO)</sub> Voltage (V) |

|-------------|-------------|----------------------------------|

| 00 0000     | 0x00        | 0.90                             |

| 00 0001     | 0x01        | 0.95                             |

| 00 0010     | 0x02        | 1.00                             |

| 00 0011     | 0x03        | 1.05                             |

|             |             |                                  |

| 00 0110     | 0x06        | 1.20                             |

|             |             |                                  |

| 00 1100     | 0x0C        | 1.50                             |

|             | •••         |                                  |

| 01 0010     | 0x12        | 1.80                             |

|             |             |                                  |

| 10 0000     | 0x20        | 2.50                             |

|             |             |                                  |

| 10 1010     | 0x2A        | 3.00                             |

|             |             |                                  |

| 11 0000     | 0x30        | 3.30 (default)                   |

|             |             |                                  |

| 11 1101     | 0x3D        | 3.95                             |

| 11 1110     | 0x3E        | 4.00                             |

| 11 1111     | 0x3F        | 4.05                             |

#### 0x0E: Configuration byte #4

The register 0x0E is **Read / Write** type. It configures the device behaviors as described.

#### Table 22. Register 0x0E

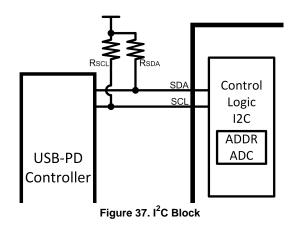

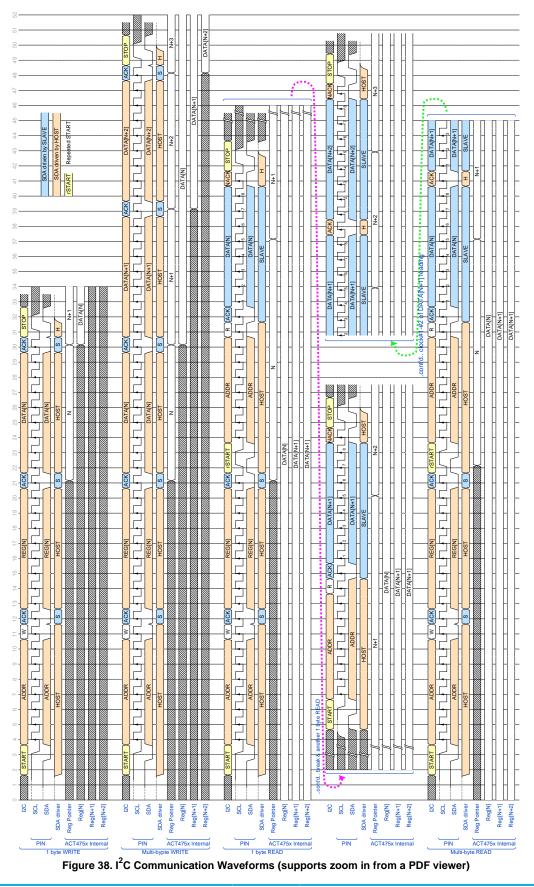

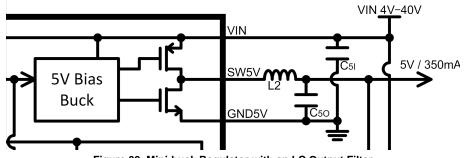

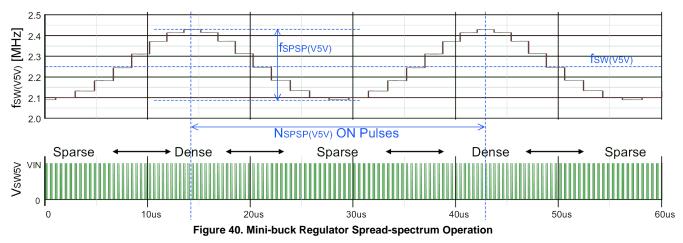

| Bit # | Bit(s) Name      | Def | Description                           |