## **Broadband Power Amplifier**

### ADM3-0022PA

### 1. Device Overview

### 1.1 General Description

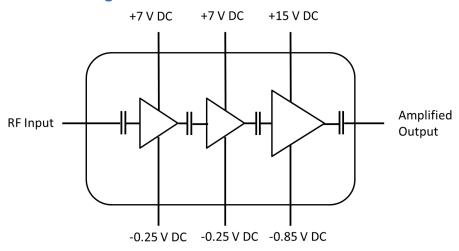

The ADM3-0022PA has the gain and output power to produce 1W of output power from a +0 dBm input power up to 22 GHz. It contains 3 broadband amplifier stages in series in a single package with built-in equalization to provide a flat gain and output power curve. This product is an unprotected amplifier module intended for lab use, see section 1.6 for a complete list of warnings.

ADM3-0022PA

ADM3-0022PA-H

### 1.2 Features

- +35 dB Small Signal Gain

- **Broadband Performance**

- +30 dBm Output Power

### 1.3 Applications

- LO Driver for Marki T3 and MT3 Mixers

- Radar

### 1.4 Functional Block Diagram

## 1.5 Part Ordering Options<sup>1</sup>

| Part<br>Number | Description                                             | Package | Green Status | Product<br>Lifecycle | Export<br>Classification |

|----------------|---------------------------------------------------------|---------|--------------|----------------------|--------------------------|

| ADM3-0022PA-H  | 0-22 GHz PA<br>Module with Heat<br>Sink                 | РА-Н    | RoHS         | Active               | EAR99                    |

| ADM3-0022PA    | 0-22 GHz PA<br>Module without<br>Heat Sink <sup>2</sup> | РА      | RoHS         | Active               | EAR99                    |

<sup>&</sup>lt;sup>1</sup> Refer to our <u>website</u> for a list of definitions for terminology presented in this table.

<sup>&</sup>lt;sup>2</sup> Customer-provided air flow cooling required for operation

### 1.6 Warnings

- The ADM3-0022PA is for use in a <u>controlled laboratory environment</u> and is **not** suitable for use in high reliability applications.

- Module may be catastrophically damaged by heat. Special care must be taken to maintain operating temperature within limits.

- Forced air cooling (such as a fan) must be continuously applied with abundant heat sinking to maintain proper operating temperature of the ADM3-0022PA-H.

- Third stage amplifier may be catastrophically damaged by incorrect sequencing or disruption of the negative supply voltage. Always sequence according to section 3.4.

- Operation of the amplifier without a load or with excessive output reflections can catastrophically damage the module. Always adhere to the maximum load VSWR in 3.1.

- Care must be taken to reduce or eliminate ESD discharge in the test environment.

- Users must rigidly adhere to absolute maximums (3.1) and sequencing procedure (3.4) to prevent catastrophic failure.

- Care must be taken to prevent damage due to excessive DC current, overheating, ESD, and damage due to large output reflections.

## **Table of Contents**

| 1. | Device Overview1                    |   |

|----|-------------------------------------|---|

|    | 1.1 General Description1            |   |

|    | 1.2 Features 1                      |   |

|    | 1.3 Applications 1                  |   |

|    | 1.4 Functional Block Diagram 1      |   |

|    | 1.5 Part Ordering Options 1         |   |

|    | 1.6 Warnings2                       | ) |

| 2. | Port Configurations and Functions 4 | ŀ |

|    | 2.1 Port Diagram4                   | ŀ |

|    | 2.2 Port Functions 5                | ) |

| 3 | . Specifications                      | Ь |

|---|---------------------------------------|---|

|   | 3.1 Absolute Maximum Ratings          | 6 |

|   | 3.2 Package Information               | 6 |

|   | 3.3 Recommended Operating Conditions. | 7 |

|   | 3.4 Sequencing Requirements           | 7 |

|   | 3.5 Electrical Specifications         | 8 |

|   | 3.6 Typical Performance Plots         | 9 |

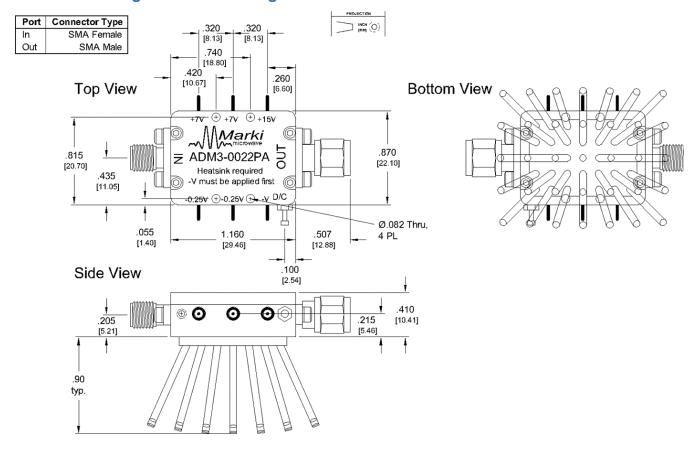

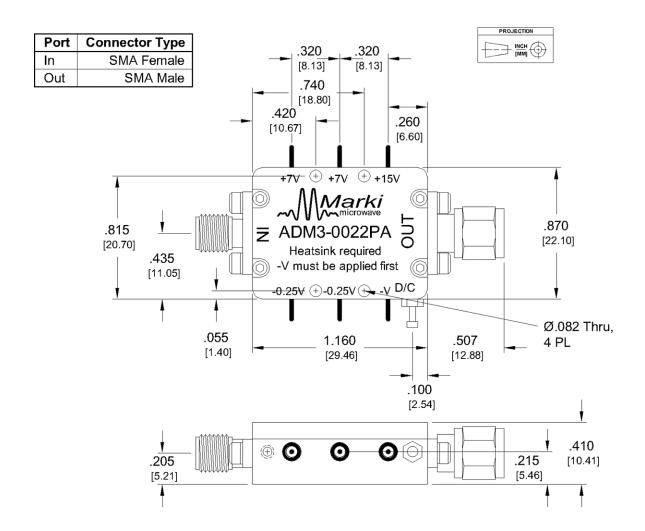

| 4 | . Mechanical Data1                    | 1 |

|   | 4.1 PA Package Outline Drawing1       | 1 |

|   | 4.2 PA-H Package Outline Drawing 18   | 2 |

**Revision History**

| Revision Code | Revision Date | Comment                   |

|---------------|---------------|---------------------------|

| -             | August 2019   | Datasheet Initial Release |

| А             | January 2020  | Format Update             |

# 2. Port Configurations and Functions

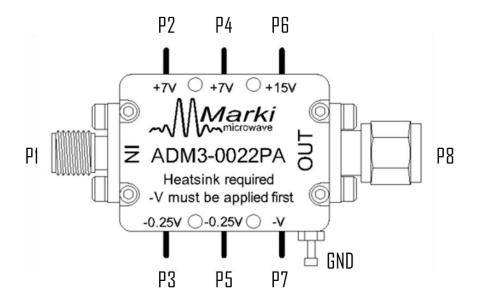

## 2.1 Port Diagram

A top-down view of the ADM3-0022PA package outline drawing is shown below. The pin functions are detailed in section 2.2 of this datasheet.

## **2.2 Port Functions**

| Port   | Function  | Description                                                                                                                                                                           | Equivalent Circuit for Package |

|--------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|

| Port 1 | RF Input  | Port 1 is the RF input of the amplifier. It is DC blocked and has a 50 $\Omega$ input impedance.                                                                                      | RF in ○→                       |

| Port 2 | Vd1       | Port 2 is the positive DC voltage supply pin for the 1 <sup>st</sup> amplifier stage. Nominally 3V – 7V, 155 mA                                                                       | y vd1                          |

| Port 3 | Vg1       | Port 3 is the negative DC voltage bias pin for the 1 <sup>st</sup> amplifier stage. Nominally - 0.25V, <1 mA                                                                          | Vg1                            |

| Port 4 | Vd2       | Port 4 is the positive DC voltage supply pin for the 2 <sup>nd</sup> amplifier stage. Nominally 3V – 7V, 155 mA                                                                       | y Vd2                          |

| Port 5 | Vg2       | Port 5 is the negative DC voltage bias pin for the 2 <sup>nd</sup> amplifier stage. Nominally - 0.25V, <1 mA                                                                          | Vg2                            |

| Port 6 | Vd3       | Port 6 is the positive DC voltage supply pin for the 3 <sup>rd</sup> amplifier stage. Nominally 13V-15V, 450 mA. <b>Vg3 must be applied to Port 7 prior to application of Vd3!</b>    | <b>y</b> Vd3                   |

| Port 7 | Vg3       | Port 7 is the negative DC voltage bias pin for the 3 <sup>rd</sup> amplifier stage. Nominally - 0.85V, <1 mA. <b>Must be applied prior to application of Vd3 on Port 6!</b>           | Vg3                            |

| Port 8 | RF Output | Port 8 is the RF output of the amplifier. It is DC blocked and has a 50 \( \Omega\) output impedance. Load must be applied to meet maximum VSWR spec.                                 | RF out                         |

| GND    | GND       | Must be connected to a DC/RF ground potential with high thermal and electrical conductivity. Ensure that the ground voltage is a common reference potential to all DC power supplies. | GND                            |

# 3. Specifications

## 3.1 Absolute Maximum Ratings

The Absolute Maximum Ratings indicate limits beyond which damage may occur to the device. If these limits are exceeded, the device may be inoperable or have a reduced lifetime.

| Parameter                                   | Maximum Rating | Units |  |

|---------------------------------------------|----------------|-------|--|

| RF Input Power (Port 1)                     | +5             | dBm   |  |

| Positive Bias Current 1 (Port 2)            | 275            | mA    |  |

| Positive Bias Voltage 1 (Port 2)            | 9              | V     |  |

| Negative Bias Voltage 1 (Port 3)            | -2             | V     |  |

| Positive Bias Current 2 (Port 4)            | 275            | mA    |  |

| Positive Bias Voltage 2 (Port 4)            | 9              | V     |  |

| Negative Bias Voltage 2 (Port 5)            | -2             | V     |  |

| Positive Bias Current 3 (Port 6)            | 500            | mA    |  |

| Positive Bias Voltage 3 (Port 6)            | 15             | V     |  |

| Negative Bias Voltage 3 (Port 7)            | -3             | V     |  |

| Output Load VSWR                            | 7:1            | -     |  |

| Case Temperature <sup>3</sup>               | -40 to +60     | °C    |  |

| Ambient Air Temperature (with PA-H Package) | -40 to +40     | °C    |  |

| Storage Temperature                         | -65 to +125    | °C    |  |

## 3.2 Package Information

| Parameter | Details                                              |       |

|-----------|------------------------------------------------------|-------|

| ESD       | Human Body Model (HBM), per MIL-STD-750, Method 1020 | 1A    |

| Weight    | PA-H Package                                         | 44.5g |

| Weight    | PA Package                                           | 19.9g |

\_

$<sup>^{\</sup>rm 3}$  Air flow across heat sink required to maintain case temperature below limits.

### 3.3 Recommended Operating Conditions

The Recommended Operating Conditions indicate the limits, inside which the device should be operated, to guarantee the performance given in Electrical Specifications. Operating outside these limits may not necessarily cause damage to the device, but the performance may degrade outside the limits of the electrical specifications. For limits, above which damage may occur, see Absolute Maximum Ratings. To keep the temperature below 60°C, the user is advised to use a fan to keep a constant airflow over the heat sink.

|                                           | Min | Nominal | Max | Units |

|-------------------------------------------|-----|---------|-----|-------|

| T <sub>A</sub> , Ambient Temperature      | -40 | +25     | +40 | °C    |

| Positive DC Voltage (Port 2, Port 4)      | +3  | +7      | +7  | V     |

| Positive DC Current (Port 2, Port 4)      | 100 | 155     | 275 | mA    |

| Positive DC Voltage (Port 6)              | +12 | +15     | +15 | V     |

| Positive DC Current (Port 6) <sup>4</sup> | 200 | 450     | 500 | mA    |

### 3.4 Sequencing Requirements

The output stage of this module uses an amplifier IC which requires a sequenced turn-on and turn-off procedure.

### Turn-on:

- 1. Ensure port 8 (RF output) is connected to load

- 2. Apply -1V to port 7 (Vg3)

- 3. Ramp port 6 (Vd3) to operating voltage

- 4. a. Apply -0.25 V to port 5 (Vg2)

- b. Apply -0.25 V to port 3 (Vg1)

- 5. a. Apply + V to port 4 (Vd2)

- b. Apply + V to port 2 (Vd1)

- 6. Apply RF power to port 1 (RF in)

- 7. Reduce port 7 negative voltage until port 6 supply current is 500 mA (limit current source to 500 mA)

### Turn-off:

- 1. Increase negative supply voltage on Port 7 back to -1V

- 2. Turn off RF power

- 3. a. Remove voltage from port 2 (Vd1)

- b. Remove voltage from port 4 (Vd2)

- 4. a. Remove voltage from port 3 (Vg1)

- b. Remove voltage from port 5 (Vg2)

- 5. Remove voltage from port 6 (Vd3)

- 6. Remove voltage from port 7 (Vg3)

- 7. Remove load from Port 8 (RF output)

-

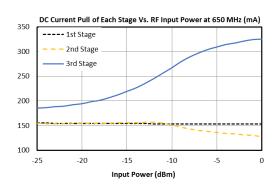

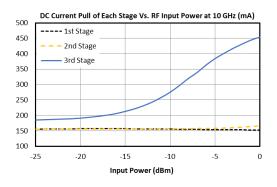

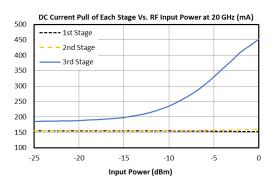

<sup>&</sup>lt;sup>4</sup> To protect the output stage of the module, ensure that Port 6 never pulls more than 500 mA of DC current. Current pull will increase with increased RF input power and with decreased negative bias on Port 7.

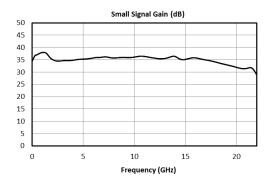

## 3.5 Electrical Specifications

The electrical specifications apply at  $T_A = +25^{\circ}C$  in a  $50\Omega$  system.

Min and Max limits apply only to our connectorized units and are guaranteed at  $T_A=+25\,^{\circ}C$ .

| Parameter               | Test Conditions                                          | Min | Typical | Units |

|-------------------------|----------------------------------------------------------|-----|---------|-------|

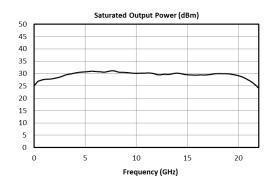

| Saturated Output Power  | 7V/-0.25V, 7V/-0.25V, 15V/-0.85V, -5 dBm<br>Input Power  | 25  | 30      | dBm   |

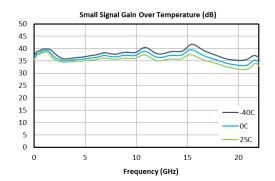

| Small Signal Gain       |                                                          | 28  | 35      |       |

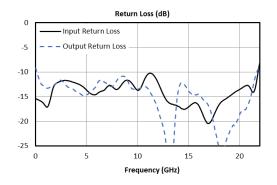

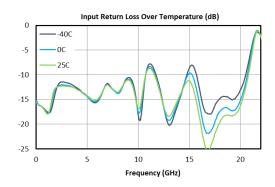

| Input Return Loss       |                                                          |     | 14      |       |

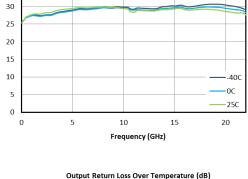

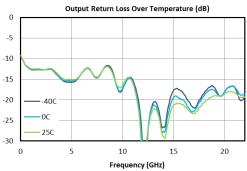

| Output Return Loss      | 7V/-0.25V, 7V/-0.25V, 15V/-0.85V, -25 dBm<br>Input Power |     | 14      | dB    |

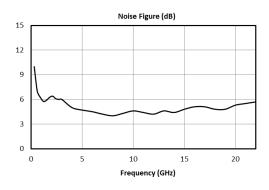

| Noise Figure            |                                                          |     | 5       |       |

| Reverse Isolation       |                                                          |     | >70     |       |

|                         | 7V/-0.25V (Ports 2/3), no RF                             |     | 155     |       |

| Bias Requirements       | 7V/-0.25V (Ports 4/5), no RF                             |     | 155     | mΑ    |

|                         | 15V/-0.85 (Ports 6/7), no RF                             |     | 185     |       |

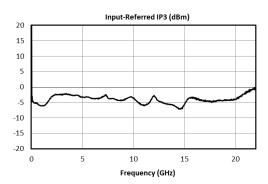

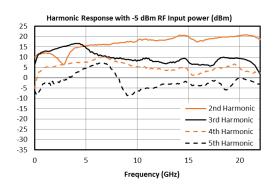

| Input IP3 (IIP3)        | 7V/-0.25V, 7V/-0.25V, 15V/-0.85V, -25 dBm<br>Input Power |     | -4      |       |

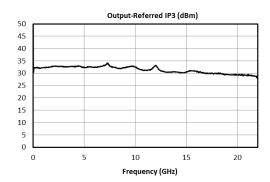

| Output IP3 (OIP3)       | 7V/-0.25V, 7V/-0.25V, 15V/-0.85V, -25 dBm<br>Input Power |     | 31      | dBm   |

| Output P <sub>1dB</sub> | 7V/-0.25V, 7V/-0.25V, 15V/-0.85V                         |     | 26      |       |

## **3.6 Typical Performance Plots**

35

Saturated Power Output Over Temperature (dBm)

## 4. Mechanical Data

## **4.1 PA Package Outline Drawing**

## 4.2 PA-H Package Outline Drawing