# **ClampZero** Family

Active Clamp IC with Integrated High-Voltage Switch Pairs with InnoSwitch4 Family of Offline Switcher ICs

## **Product Highlights**

#### **Highly Integrated, Compact Footprint**

- Eliminates switching losses in InnoSwitch4 primary switch

- · Captures and recycles leakage inductance energy

- Dramatically improves power supply efficiency

- · Interfaces seamlessly with InnoSwitch4

- Powered directly from InnoSwitch4 BYPASS pin

- Self-biased at start-up

- Operates in both DCM and CCM modes

#### **Advanced Protection / Safety Features**

• Integrated temperature sensing and hysteretic thermal shutdown

#### **Green Package**

· Halogen free and RoHS compliant

#### **Applications**

· High density flyback designs up to 135 W

#### Description

The ClampZero™ IC pairs with the InnoSwitch™4 family of ICs to eliminate energy wasted due to switching losses in the clamp and primary switch. This dramatically improves power supply efficiency – easily exceeding 95% - while maintaining the flexibility and low component count of the flyback architecture.

The ClampZero IC is an active clamping circuit which recycles otherwise wasted leakage inductance energy. The ClampZero incorporates a high-side power switch and level shifted self-biased controller which receives communication from a low-side transceiver connected to the InnoSwitch4 primary controller

By ensuring zero voltage switching across all line and load conditions and in both CCM and DCM operating modes, ClampZero combines with InnoSwitch4 to implement a highly flexible active clamp flyback solution. In a typical application paired with the InnoSwitch4 IC, the low switching losses permit use of a high switching frequency, minimizing the physical size of the transformer and resulting in an extremely small PCB footprint.

Zero-voltage switching is achieved by precise timing between the turn-off of the ClampZero and turn-on of the InnoSwitch4 power switch, which completely removes turn-on losses. The overall effect of this synchronized switching, along with the InnoSwitch4 PowiGaN switch with zero turn-off losses, is a flyback converter with zero primary clamp losses and zero power switch switching losses enabling high density, heatsinkless flyback designs up to 135 W.

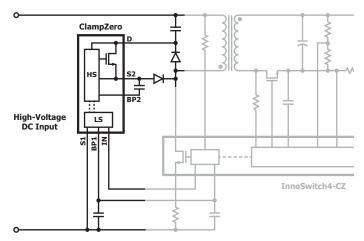

Figure 1. Typical Application schematic.

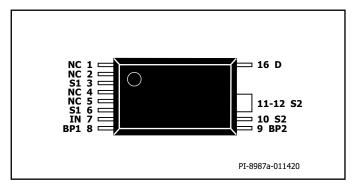

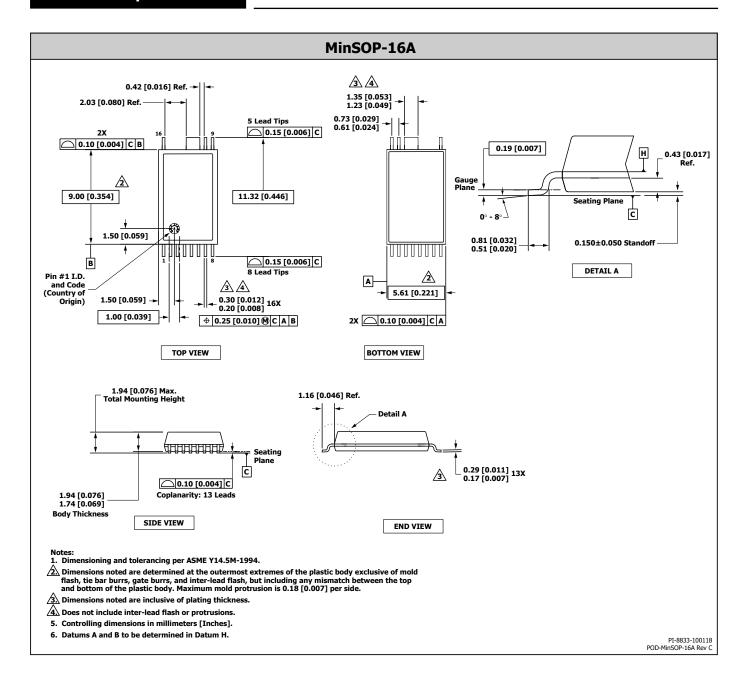

Figure 2. MinSOP-16A Package with Creepage for High-Side Driver.

### ClampZero + InnoSwitch4 Output Power Table

| Product <sup>3</sup> | 85-265 VAC           |                         |  |

|----------------------|----------------------|-------------------------|--|

|                      | Adapter <sup>1</sup> | Open Frame <sup>2</sup> |  |

| CPZ1061M             | 75 W                 | 85 W                    |  |

| CPZ1062M             | 120 W                | 135 W                   |  |

Table 1. Output Power Table. Notes:

- 1. Minimum continuous power in a typical non-ventilated enclosed typical size adapter measured at 40  $^{\circ}$ C ambient. Max output power is dependent on the design. With condition that package temperature must be < 125  $^{\circ}$ C.

- 2. Minimum peak power capability.

- 3. Package: MinSOP-16A.

www.power.com November 2020

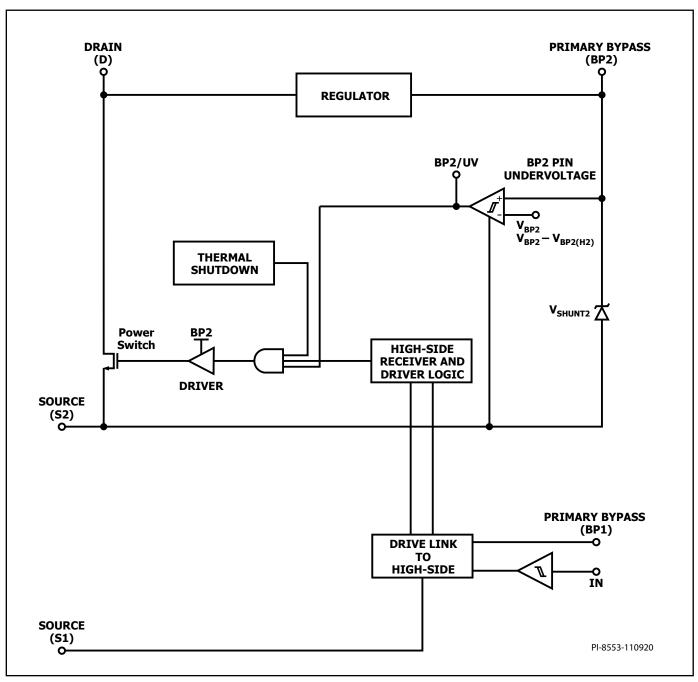

Figure 3. Block Diagram.

#### **Pin Functional Description**

#### Not Connected (NC) Pin (Pins 1-2, 4-5)

These pins are not electrically connected. Pin 5 must connect to S1 pin.

#### LOW-SIDE SOURCE (S1) Pin (Pins 3 and 6)

Source connection of low-side controller.

### **LOW-SIDE RECEIVER (IN) Pin (Pin 7)**

Receiver for Clamp Zero trigger; connects to HSD pin of InnoSwitch4.

### **LOW-SIDE BYPASS (BP1) Pin (Pin 8)**

Supply voltage for low side controller. Needs to be connected to BPP of InnoSwitch4 primary to draw power from auxiliary winding.

#### **HIGH-SIDE BYPASS (BP2) Pin (Pin 9)**

Supply voltage for high-side controller.

# HIGH-SIDE SOURCE (S2) Pin (Pins 10-12)

Source connection of high-side switch.

#### DRAIN (D) Pin (Pin 16)

Drain of high-side switch.

#### **ClampZero Functional Description**

The ClampZero integrates low-side and high-side controller, plus a high-side power switch with gate driver.

The ClampZero is the partner IC with InnoSwitch4 to provide zero voltage switching (ZVS) functionality to the main power switch of flyback power converter. The ClampZero IC operates as an active clamping circuit in a flyback power supply that has the ability to operate in continuous conduction mode (CCM) and discontinuous conduction mode (DCM). The ClampZero incorporates a high-side power switch and self-biasing controller with integrated thermal protection, low-to-high side communication and low-side transceiver to receive a clamp turn-on signal from the InnoSwitch4 primary controller.

Figure 3 shows the functional block diagram of the controller, highlighting the most important features.

#### **LOW-SIDE BYPASS Pin**

Low-side controller receives its bias for BP1 from InnoSwitch4 BPP pin. When BP1 voltage is  $V_{\text{BP1}(\text{RESET})1}$  or greater, low-side controller is functional and able to receive an HSD pulse from InnoSwitch4 and communicate the drive instruction to the high-side driver stage.

#### **LOW-SIDE RECEIVER Pin**

The ClampZero low-side controller receives signal from InnoSwitch4 HSD pin. During the rising edge of the signal, the low-side controller communicates the drive instruction to turn on the high-side switch when HSD signal is above  $V_{_{\rm IN(R)}}$ . During the falling edge of the signal, the low-side controller communicates the drive instruction to turn off the high-side switch when HSD signal is below  $V_{_{\rm IN(F)}}$ .

#### **HIGH-SIDE BYPASS Pin Regulator**

High-side BYPASS pin has an internal regulator that charges the BP2 to  $V_{\text{BP2}}$  by drawing current from the DRAIN pin whenever the power switch is off. The amount of charge current available for BP2 is important in order to have fast start-up from initial switching of

Figure 4. Pin Configuration.

InnoSwitch4. Thus the BP2 capacitor value is limited to 150 nF (min 100 nF/max 220 nF). Higher value BP2 capacitor is undesirable as this would cause too much delay in start-up and cause possible overshoot of primary clamp voltage.

#### **HIGH-SIDE BYPASS Pin Undervoltage Threshold**

The BP2 pin undervoltage circuitry disables the power switch when the BP2 pin voltage drops below  $\sim\!4.4$  V (VBP2 – VBP2(H2)) in steady-state operation. Once the BP2 pin voltage falls below this threshold, it must rise to VBP2 to re-enable turn-on of the power switch.

In addition, a shunt regulator clamps BP2 pin voltage to  $V_{\text{SHUNT2}}$  when current is provided to the BP2 through external bias winding or boot strap circuit. This would remove the excessive dissipation on the BP2 charge current from DRAIN pin during steady state.

#### **Over-Temperature Protection**

The thermal shutdown circuitry senses the die temperature. If the die temperature rises above the threshold, the power switch is disabled and remains disabled until the die temperature falls by  $T_{\text{SD(H)}}$  at which point switching is re-enabled. A large amount of hysteresis is provided to prevent over-heating of the PCB due to a continuous fault condition.

#### Zero Voltage Switching (ZVS)

InnoSwitch4 will achieve ZVS operation both in CCM and DCM operation with ClampZero providing extra high side switch. The operation of the converter is as:

- InnoSwitch4, after receiving the Flux Link pulse, does not immediately turn on primary switch.

- InnoSwitch4 primary controller first generates a fixed duration pulse on the HSD pin. This pulse will control the power switch inside ClampZero, and the switch will be turned on when HSD pulse is high. ClampZero starts recycling clamp capacitor energy to output and also building up energy on transformer magnetizing inductance and leakage inductance which are used later for ZVS.

- After InnoSwitch4 terminates the HSD pulse, it waits for additional delay and then turns on the primary switch. This delay is programmable by InnoSwitch4. During this delay, the energy built up at magnetizing inductance and leakage inductance will help discharge C<sub>oss</sub> of primary switch in InnoSwitch4 to achieve ZVS.

### **Applications Example**

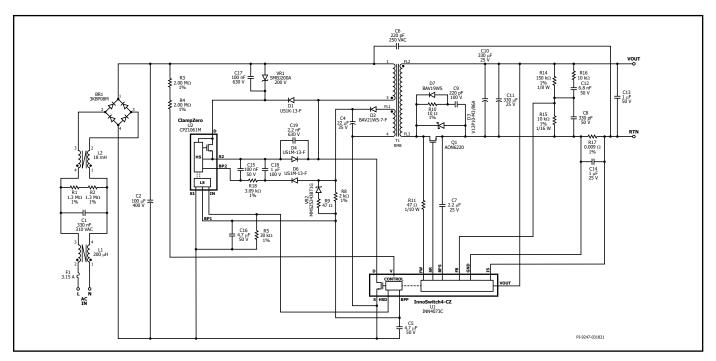

Figure 5. Schematic 20 V / 3.25 A Notebook Adapter Power Supply.

The circuit shown in Figure 5 is a 20 V, 3.25 A single output power supply using INN4073C and CPZ1061M. This single output design is DOE Level 6 and EC CoC v5 compliant.

Input fuse F1 isolates the circuit and provides protection from component failure, and the common mode choke L1 and L2 with capacitor C1 attenuation for EMI. Bridge rectifier BR1 rectifies the AC line voltage and provides a full wave rectified DC across the filter capacitor C2. Y capacitor C6 connected between the power supply output and input helps to reduce common mode EMI.

Resistors R1 and R2 along with U2 discharge capacitor C1 when the power supply is disconnected from AC mains.

One end of the transformer primary is connected to the rectified DC bus; the other is connected to the drain terminal of the switch inside the InnoSwitch4 IC (U1). Resistors R3 and R4 provide input voltage sense protection for undervoltage and overvoltage conditions.

The primary clamp formed by diode D1 and capacitor C17 limits the peak drain voltage of U1 at the instant of turn-off of the switch inside U1. The energy stored in the leakage inductance of transformer T1 will be transferred to capacitor C17. Part of the magnetizing energy will also get transferred to C17 depending on the capacitance value used. VR1 is used to protect the InnoSwitch4 from excessive drain voltages if there is any malfunction of the power supply.

When the FluxLink™ signal is received from the secondary-side, the InnoSwitch4 generates an HSD signal to turn on the ClampZero device. When the ClampZero IC (U2) turns on, to achieve soft switching of the InnoSwitch4 primary switch, clamp capacitor C17 starts to charge the leakage inductance of the transformer in the case of CCM operation and both the leakage and the magnetizing inductance of the transformer in the case of DCM operation. Ultrafast diodes D1 and D4 are used to divert the transformer current from the body diode of ClampZero's high-side switch to minimize the reverse-recovery energy. A small delay is provided from the instant the

high-side switch turns off in order to achieve zero voltage switching on the primary switch. This delay is programmable by different resistor values of R5. Capacitor C19 will help reduce the voltage on the ClampZero IC (U2) to provide soft turn-on.

Capacitor C16 is used to provide local decoupling at the BP1 pin. Capacitor C15 provides the decoupling for BP2 pin. Diode D6 and capacitor C18 form a bootstrap circuit to provide the bias for the high-side BP2 pin. Resistor R18 limits the current flowing into the BP2 pin.

The InnoSwitch4 IC is self-starting, using an internal high-voltage current source to charge the PRIMARY BYPASS pin capacitor (C5) when AC is first applied. During normal operation, the primary-side block is powered from an auxiliary winding on the transformer T1. Output of the auxiliary (or bias) winding is rectified using diode D2 and filtered using capacitor C4. Resistor R8 limits the current being supplied to the PRIMARY BYPASS pin of InnoSwitch4 IC (U1).

Output regulation is achieved using modulation control, where the frequency and ILIM of switching cycles are adjusted based on the output load. At high load, most switching cycles are enabled for a high value of ILIM in the selected ILIM range, and at light load or no-load, most cycles are disabled, and the ones enabled have a low value of ILIM in the selected ILIM range. Once a cycle is enabled, the switch remains on until the primary current ramps to the device current limit for the specific operating state.

The latch-off/auto-restart primary-side overvoltage protection is obtained using Zener diode VR2 with current limiting resistor R9. In a flyback converter, output of the auxiliary winding tracks the output voltage of the converter. In case of overvoltage at the output of the converter, the auxiliary winding voltage increases and causes breakdown of VR2, which then causes a current to flow into the BPP pin of InnoSwitch4 IC U1. If the current flowing into the BPP pin increases above the ISD threshold, the U1 controller latches off to prevent any further increase in output voltage.

Dower

The secondary-side of the InnoSwitch4 IC provides output voltage, output current sensing, and drive to a MOSFET providing synchronous rectification. The secondary of the transformer is rectified by SR FET Q1/D3 and filtered by capacitors C10 and C11. Capacitor C13 is used to reduce the high-frequency output voltage ripple. High-frequency ringing during switching transients that would otherwise create radiated EMI is reduced via RCD snubber R10, C9, and D7. Diode D7 minimizes the dissipation in resistor R10.

The gate of Q1 is turned on by the secondary-side controller of IC U1, based on the winding voltage sensed via resistor R11 and fed into the FWD pin of the IC.

In continuous conduction mode of operation, the SR MOSFET is turned off just prior to the secondary-side commanding a new switching cycle from the primary. In discontinuous mode of operation, the power MOSFET is turned off, when the voltage drop across the MOSFET falls below a threshold of approximately  $V_{\text{SR(TH)}}$  mV.

The secondary side of the IC U1 is self-powered from either the secondary winding forward voltage or the output voltage. Capacitor C7 connected to the BPS pin of IC U1 provides decoupling for the internal circuitry.

Below the CC threshold, the device operates in constant voltage mode. During constant voltage mode operation, output voltage regulation is achieved through sensing the output voltage via divider resistors R14 and R15. The voltage across R15 is fed into the FEEDBACK pin with an internal reference voltage threshold of 1.265 V. The output voltage is regulated so as to achieve a voltage of 1.265 V on the FEEDBACK pin. Capacitor C8 provides noise filtering of the signal at the FEEDBACK pin.

During CC operation, when the output voltage falls, the device directly powers itself from the secondary winding. During the on-time of the primary-side power switch, the forward voltage that appears across the secondary winding is used to charge the decoupling capacitor C7 via resistor R11 and an internal regulator. This allows output current regulation to be maintained down to  $\sim\!\!3.4$  V. Output current is sensed by monitoring the voltage drop across resistor R17 between the IS and SECONDARY GROUND pins. A threshold of approximately 35 mV reduces losses. C14 provides filtering on the IS pin from external noise. Once the internal current sense threshold is exceeded, the device regulates the number of switch pulses to maintain a fixed output current.

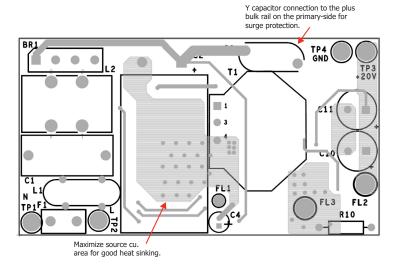

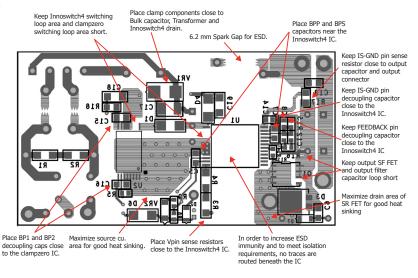

### **Layout Example**

Figure 6. PCB Layout Top Side.

Figure 7. PCB Layout Bottom Side.

### **Key Application Considerations**

#### **No-load Consumption**

The ClampZero device draws energy from the BP1 pin decoupling capacitor, which is supplied by the internal tap of InnoSwitch4. The InnoSwitch-4 IC can start in self-powered mode, drawing energy from the BYPASS pin capacitor charged through an internal current source. Use of a bias winding, however, is required to provide supply current to the PRIMARY BYPASS pin, once the InnoSwitch4 IC has started switching. An auxiliary (bias) winding provided on the transformer serves this purpose. The high-side BP2 pin decoupling capacitor of the ClampZero device draws energy from the internal tap, once the power supply starts switching. In order to minimize the no-load consumption, a bootstrap diode D6 is recommended. Resistors R8 and R18 shown in Figure 5 should be adjusted to achieve the lowest no-load input power. ClampZero typically consumes  $\sim\!\!35~\mu\text{A}$  from the BP1 pin and  $\sim\!\!50~\mu\text{A}$  from the BP2 pin at no-load, adding only a few mW to total system losses.

# **Critical Components Selection**

#### **BP2 Pin Decoupling Capacitor**

The high-side BYPASS pin has an internal regulator that charges BP2 to VBP2 by drawing current from the DRAIN pin whenever the power switch is off. The amount of charge current available for BP2 is important in order to have fast start-up from initial switching of InnoSwitch-4. Thus, the BP2 capacitor value is set to 150 nF. A higher value BP2 capacitor is undesirable, because too much start-up delay may cause overshoot of the primary clamp voltage. A 100 nF to 220 nF capacitor may be used. At least 10 V, 0603 or larger size rated X5R or X7R dielectric capacitors are recommended to ensure that minimum capacitance requirements are met. The ceramic capacitor type designations, such as X7R or X5R from different manufacturers or different product families, do not have the same voltage coefficients. It is recommended that capacitor data sheets be reviewed to ensure that the selected capacitor will not have more than 20% drop in capacitance at 5 V. Do not use Y5U or Z5U / 0402 rated MLCC, because this type of SMD ceramic capacitor has very poor voltage and temperature coefficient characteristics.

#### **Bias Winding and External Bias Circuit**

The internal regulator connected from the DRAIN pin of the switch to the PRIMARY BYPASS pin of the InnoSwitch4 primary-side controller charges the capacitors connected to the InnoSwitch4 BPP pin and ClampZero BP1 pin to achieve start-up. A bias winding should be provided on the transformer with a suitable rectifier and filter capacitor to create a bias supply that can be used to supply current to the BPP and BP1 pins. The turns ratio for the bias winding should be selected such that a minimum of  ${\sim}8~\rm V$  is developed across the bias winding at the lowest rated output voltage of the power supply at the lowest load condition. If the voltage is lower than this, no-load input power increases.

The bias current from the external circuit should be set to  $I_{\text{SI(MAX)}}$  to achieve lowest no-load power consumption when operating the power supply at 230 VAC input, (V $_{\text{BPP}} > 5$  V). A glass passivated standard recovery rectifier diode with low junction capacitance is recommended to avoid the snappy recovery typically seen with fast or ultrafast diodes that can lead to higher radiated EMI. An aluminum capacitor of at least 22  $\mu\text{F}$  with a voltage rating 1.2 times greater than the highest voltage developed across the capacitor is recommended. Highest voltage is typically developed across this capacitor when the supply is operated at the highest rated output voltage and load with the lowest input AC supply voltage.

#### **Clamp Capacitor**

It is recommended to choose the value of the clamp capacitor such that  ${\sim}0.25$  times the resonant period of the  $C_{\text{CLAMP}}$  and  $L_{\text{LKG}}$  equals the HSD pulse width for CCM designs, and  ${\sim}0.5$  times the resonant period of the  $C_{\text{CLAMP}}$  and  $L_{\text{LKG}}$  equals the HSD pulse width in the case of DCM-only designs. Capacitance in the range of 10 nF to 100 nF may be used depending on the design. At least 200 V, 1206 or larger size rated X7R dielectric capacitors are recommended.

For CCM designs

HSD Pulse Width

$$\sim \frac{\pi}{2} \sqrt{L_{LKG} C_{CLAMP}}$$

For DCM designs

HSD Pulse Width

$$\sim \pi \sqrt{L_{LKG}C_{CLAMP}}$$

# **Layout Considerations**

The following layout considerations are specifically for the ClampZero components. For placement and layout of InnoSwitch4 specific and power components, check the InnoSwitch4 data sheet.

- The ClampZero BP1 pin is supplied and regulated by the InnoSwitch4 internal BPP regulator. A separate decoupling capacitor needs to be placed very close to the BP1 pin of the ClampZero device.

- The high-side BP2 pin is supplied by the internal drain tap during startup until the external bias is available from an external bootstrap circuit. A decoupling capacitor should be placed very close to the BP2 pin of the ClampZero IC.

- Even though ClampZero conducts only for a short period and dissipates a small amount of power, some amount of PCB copper heatsinking on the source pin of the ClampZero device is required to minimize the thermals.

- It is recommended to place the bootstrap components close to the BP2 and SOURCE pins of the ClampZero device to minimize the noise coupling into other parts of the circuit.

- Place the ClampZero IC as close as possible to the clamp capacitor and transformer to minimize the clamp loop area.

Figure 2 shows the ClampZero layout used for the design in Figure 5 following the recommendations stated above.

#### **Quick Design Checklist**

Aside from the verification of the functionality of the InnoSwitch-4 IC, proper operation of the ClampZero IC must also be checked. At the minimum, the following verification tests must be performed.

- Maximum Drain Voltage Verify that VDS of ClampZero does not exceed 90% of the breakdown voltage at the highest input voltage and peak (overload) output power in normal operation and during start-up.

- Maximum Drain Current Under all conditions, the maximum drain current for the ClampZero switch should be below the specified absolute maximum rating.

- 3. Thermal Check Verify that the ClampZero IC does not cause an OTP fault when operating at maximum load throughout the whole input range. Sufficient bias current needs to be supplied to the BP2 pin of the ClampZero device; otherwise, operating with the internal tap can result in higher dissipation on the ClampZero device and eventually reach extreme operating conditions. Triggering OTP of the ClampZero device can cause additional thermal stress on the InnoSwitch-4 device and the TVS device used across the clamp capacitor because of loss of zero voltage switching. This can also increase voltage stress on the DRAIN pin of the InnoSwitch4 and ClampZero devices.

Dower

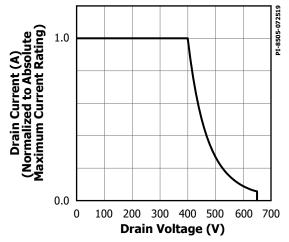

#### Absolute Maximum Ratings1,2

| DRAIN to S2 Pin Voltage: CPZ1061M & CPZ1062M | 0.3 to 650 V        |

|----------------------------------------------|---------------------|

| DRAIN Pin Peak Current: CPZ1061M             | 3.26 A <sup>3</sup> |

| CPZ1062M                                     | 3.87 A <sup>3</sup> |

| BP1 to S1 Pin Voltage                        | 0.3 V to 6 V        |

| IN to S1 Pin Voltage                         | 0.3 V to 6 V        |

| BP2 to S2 Pin Voltage                        | 0.3 V to 6 V        |

| S2 to S1 Pin Voltage                         | 0.3 V to 650 V      |

| Storage Temperature                          | 65 to 150 °C        |

| Operating Junction Temperature <sup>4</sup>  | 40 to 150 °C        |

| Ambient Temperature                          | 40 to 105 °C        |

| Lead Temperature <sup>5</sup>                | 260 °C              |

#### Notes:

- 1. All voltages referenced to low-side or high-side source,  $T_A$  = 25 °C.

- Maximum ratings specified may be applied one at a time without causing permanent damage to the product. Exposure to Absolute Maximum Ratings conditions for extended periods of time may affect product reliability.

- 3. Please refer to Figure 8 about maximum allowable voltage and current combinations.

- 4. Normally limited by internal circuitry.

- 5. 1/16" from case for 5 seconds.

#### **Thermal Resistance**

Thermal Resistance:

#### Notes:

- 1. Case termperature measured at top center of package body.

- 2. Solder to 0.36 sq. in (232 mm<sup>2</sup>), 2 oz. (610 g/m<sup>2</sup>) copper clad.

- 3. Solder to 1 sq. in (645 mm<sup>2</sup>), 2 oz. (610 g/m<sup>2</sup>) copper clad.

| Parameter                               | Symbol                   | Conditions  SOURCE = 0 V $T_{_{J}}$ = -40 °C to 125 °C  (Unless Otherwise Specified)             |          | Min  | Тур  | Max  | Units |

|-----------------------------------------|--------------------------|--------------------------------------------------------------------------------------------------|----------|------|------|------|-------|

| Control Functions                       |                          |                                                                                                  |          |      |      |      |       |

| BP2 Supply Current                      | I <sub>S1(2)</sub>       | VBP2 = VBP2 + 0.1 V<br>(Switch not Switching)<br>$T_{_{\rm J}} = 25  ^{\circ}\text{C}$           |          | 35   | 47   | 55   | μΑ    |

|                                         | I <sub>S2(2)</sub>       | $VBP2 = VBP2 + 0.1 V$ (Switch Switching at $f_{OSC} = 180 \text{ kHz}$ ) $T_{J} = 25 \text{ °C}$ | CPZ1061M | 400  | 580  | 800  | μΑ    |

|                                         |                          |                                                                                                  | CPZ1062M | 600  | 760  | 950  |       |

| BP2 Pin Charge Current                  | I <sub>CH1(2)</sub>      | VBP2 = 0 V<br>T <sub>3</sub> = 25 °C                                                             |          | 4.2  | 5.2  | 6.2  | - mA  |

|                                         | I <sub>CH2(2)</sub>      | VBP2 = 4 V<br>T <sub>J</sub> = 25 °C                                                             |          | 4.2  | 5.2  | 6.2  |       |

| BP2 Pin Voltage                         | V <sub>BP2</sub>         |                                                                                                  |          | 4.8  | 5    | 5.2  | V     |

| BP2 Pin Voltage<br>Hysteresis           | V <sub>BP2(H2)</sub>     |                                                                                                  |          | 0.38 | 0.6  | 0.8  | V     |

| BP2 Shunt Voltage                       | V <sub>SHUNT2</sub>      | IBP2 = 2 mA                                                                                      |          | 5.2  | 5.45 | 5.7  | V     |

| BP2 Power-Up Reset<br>Threshold voltage | V <sub>BP2(RESET)2</sub> | T <sub>3</sub> = 25 °C                                                                           |          | 3    | 3.23 | 3.45 | V     |

+Dower 5

| Parameter                               | Symbol                     | Conditions  SOURCE = 0 V $T_{_{J}}$ = -40 °C to 125 °C  (Unless Otherwise Specified)                       | Min      | Тур      | Max      | Units |  |

|-----------------------------------------|----------------------------|------------------------------------------------------------------------------------------------------------|----------|----------|----------|-------|--|

| Control Functions (cont.)               |                            |                                                                                                            |          |          |          |       |  |

| BP1 Power-Up Reset<br>Threshold voltage | V <sub>BP1(RESET)2</sub>   | T <sub>3</sub> = 25 °C                                                                                     | 3.4      | 3.8      | 4.2      | V     |  |

| BP1 Supply Current<br>(Load)            | I <sub>S1(1)</sub>         | Non Switching, $V_{BP1} = 5.1 \text{ V}$<br>IN: 0 V<br>$T_{J} = 25 \text{ °C}$                             | 20       | 30       | 50       | μА    |  |

|                                         | I <sub>S2(1)</sub>         | Switching, IN: 500 ns Pulse at 180 kHz $ V_{\text{BP1}} = 5.1 \text{ V}                                  $ | 60       | 80       | 100      | μА    |  |

| IN Pin Voltage Rising<br>Threshold      | V <sub>IN(R)</sub>         |                                                                                                            | 2.75     | 2.93     | 3.25     | V     |  |

| IN Pin Voltage Falling<br>Threshold     | V <sub>IN(F)</sub>         |                                                                                                            | 1.6      | 1.82     | 2.1      | V     |  |

| Delay from HSD High to<br>ClampZero ON  | D <sub>HSD(ON)</sub>       |                                                                                                            | 30       | 57       | 100      | ns    |  |

| Delay From HSD Low To<br>ClampZero OFF  | D <sub>HSD(OFF)</sub>      | CPZ1061M<br>CPZ1062M                                                                                       | 35<br>42 | 55<br>62 | 80<br>90 | ns    |  |

| Circuit Protection                      |                            |                                                                                                            | ·-       |          |          |       |  |

| Thermal Shutdown                        | T <sub>SD</sub>            |                                                                                                            | 135      | 142      | 150      | °C    |  |

| Thermal Shutdown<br>Hysteresis          | T <sub>SD(H)</sub>         |                                                                                                            |          | 70       |          | °C    |  |

| <b>Electrical Characteristics</b>       |                            |                                                                                                            |          |          |          |       |  |

| CPZ1061M                                |                            |                                                                                                            |          |          |          |       |  |

| Off-State Drain<br>Leakage Current      | $\mathbf{I}_{	extsf{DSS}}$ | $V_{BP2} = V_{BP2} + 0.1 \text{ V}$<br>VDS = 80% Peak Drain Voltage<br>$T_{J} = 125 \text{ °C}$            |          |          | 200      | μА    |  |

| On-State Resistance                     | R <sub>DS(ON)</sub>        | $I_{D} = 300 \text{ mA}$<br>$T_{J} = 25 \text{ °C}$                                                        |          | 3.2      | 3.68     | Ω     |  |

|                                         |                            | $I_{\rm D} = 300 \text{ mA}$<br>$T_{\rm J} = 100 \text{ °C}$                                               |          | 4.96     | 5.7      |       |  |

| CPZ1062M                                |                            |                                                                                                            |          |          |          |       |  |

| Off-State Drain<br>Leakage Current      | I <sub>DSS</sub>           | $V_{BP2} = V_{BP2} + 0.1 \text{ V}$<br>VDS = 80% Peak Drain Voltage<br>$T_{J} = 125 \text{ °C}$            |          |          | 200      | μА    |  |

| On-State Resistance                     | D.                         | $I_{D} = 300 \text{ mA}$<br>$T_{J} = 25 \text{ °C}$                                                        |          | 1.95     | 2.24     | Ω     |  |

|                                         | R <sub>DS(ON)</sub>        | $I_{D} = 300 \text{ mA}$<br>$T_{J} = 100 \text{ °C}$                                                       |          | 3.02     | 3.47     | Ω     |  |

newoc

# **Typical Performance Curves**

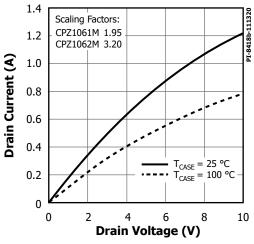

Figure 8. Maximum Allowable Drain Current vs. Drain Voltage.

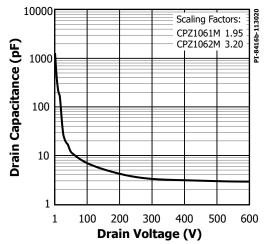

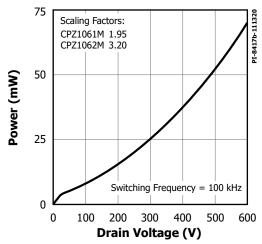

Figure 10.  $C_{\rm oss}$  vs. Drain Voltage.

Figure 9. Output Characteristics.

Figure 11. Drain Capacitance Power.

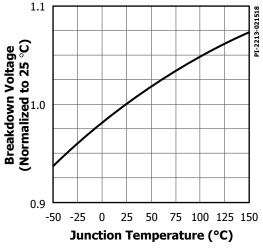

Figure 12. Breakdown vs. Temperature.

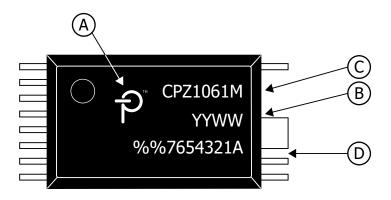

# **PACKAGE MARKING**

# MinSOP-16A

- A. Power Integrations Registered Trademark

- B. Assembly Date Code (last two digits of year followed by 2-digit work week)

- C. Product Identification (Part #/Package Type)

- D. Lot Identification Code

PI-9220a-111720

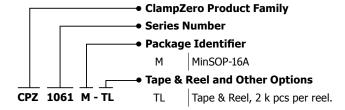

# **Part Ordering Information**

-Dower 11

| Revision | Notes           | Date  |

|----------|-----------------|-------|

| С        | Code A Release. | 11/20 |

#### For the latest updates, visit our website: www.power.com

Power Integrations reserves the right to make changes to its products at any time to improve reliability or manufacturability. Power Integrations does not assume any liability arising from the use of any device or circuit described herein. POWER INTEGRATIONS MAKES NO WARRANTY HEREIN AND SPECIFICALLY DISCLAIMS ALL WARRANTIES INCLUDING, WITHOUT LIMITATION, THE IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, AND NON-INFRINGEMENT OF THIRD PARTY RIGHTS.

#### **Patent Information**

The products and applications illustrated herein (including transformer construction and circuits external to the products) may be covered by one or more U.S. and foreign patents, or potentially by pending U.S. and foreign patent applications assigned to Power Integrations. A complete list of Power Integrations patents may be found at www.power.com. Power Integrations grants its customers a license under certain patent rights as set forth at www.power.com/ip.htm.

#### Life Support Policy

POWER INTEGRATIONS PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF POWER INTEGRATIONS. As used herein:

- A Life support device or system is one which, (i) is intended for surgical implant into the body, or (ii) supports or sustains life, and (iii) whose failure to perform, when properly used in accordance with instructions for use, can be reasonably expected to result in significant injury or death to the user.

- 2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

Power Integrations, the Power Integrations logo, CAPZero, ChiPhy, CHY, DPA-Switch, EcoSmart, E-Shield, eSIP, eSOP, HiperPLC, HiperPFS, HiperTFS, InnoSwitch, Innovation in Power Conversion, InSOP, LinkSwitch, LinkZero, LYTSwitch, SENZero, TinySwitch, TOPSwitch, PI, PI Expert, PowiGaN, SCALE, SCALE-1, SCALE-2, SCALE-3 and SCALE-iDriver, are trademarks of Power Integrations, Inc. Other trademarks are property of their respective companies. ©2020, Power Integrations, Inc.

#### **Power Integrations Worldwide Sales Support Locations**

#### **World Headquarters**

5245 Hellyer Avenue San Jose, CA 95138, USA Main: +1-408-414-9200 Customer Service:

Worldwide: +1-65-635-64480 Americas: +1-408-414-9621 e-mail: usasales@power.com

#### China (Shanghai)

Rm 2410, Charity Plaza, No. 88 North Caoxi Road Shanghai, PRC 200030 Phone: +86-21-6354-6323 e-mail: chinasales@power.com

#### China (Shenzhen)

8th Road, Nanshan District, Shenzhen, China, 518057 Phone: +86-755-8672-8689 e-mail: chinasales@power.com Germany (AC-DC/LED Sales)

Einsteinring 24

85609 Dornach/Aschheim Germany

Tel: +49-89-5527-39100 e-mail: eurosales@power.com

**Germany** (Gate Driver Sales) HellwegForum 3

59469 Ense Germany

Tel: +49-2938-64-39990 e-mail: japansales@power.com e-mail: japansales@power.com

#1, 14th Main Road Vasanthanagar 17/F, Hivac Building, No. 2, Keji Nan Bangalore-560052 India Phone: +91-80-4113-8020 e-mail: indiasales@power.com

#### **Italy**

Via Milanese 20, 3rd. Fl. 20099 Sesto San Giovanni (MI) Italy Phone: +39-024-550-8701 e-mail: eurosales@power.com

Yusen Shin-Yokohama 1-chome Bldg. Taiwan 1-7-9, Shin-Yokohama, Kohoku-ku Yokohama-shi, Kanagawa 222-0033 Japan Phone: +81-45-471-1021

RM 602, 6FL Korea City Air Terminal B/D, 159-6 Samsung-Dong, Kangnam-Gu, Seoul, 135-728, Korea Phone: +82-2-2016-6610 e-mail: koreasales@power.com

#### Singapore

51 Newton Road #19-01/05 Goldhill Plaza Singapore, 308900 Phone: +65-6358-2160 e-mail: singaporesales@power.com

5F, No. 318, Nei Hu Rd., Sec. 1 Nei Hu Dist. Taipei 11493, Taiwan R.O.C.

Phone: +886-2-2659-4570 e-mail: taiwansales@power.com

#### UK

Building 5, Suite 21 The Westbrook Centre Milton Road Cambridge

CB4 1YG

Phone: +44 (0) 7823-557484 e-mail: eurosales@power.com